連載

第30回 インターポーザ:前田真一の最新実装技術あれこれ塾(3/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第30回は基板で処理しやすいパッド間隔やピン並びに変換する中継部品「インターポーザ」について解説する。

3. インターポーザ基板

SoC(System on Chip)やMCPへの各種インタフェースやキャッシュメモリなど、1チップへの機能集積がICの微細化の以上に進んだ結果、チップの面積が増大し、と信号ピンが多くなりました。

これに合わせ、パッケージのピン数が増えると同時に、パッケージの小型化が望まれ、アレイ状のピン(ボール)を表面実装できるBGA(Ball Grid Array)パッケージが標準化されました(図13)。

さらにチップ面積とほぼ同じパッケージ面積のCSP(Chip Size BGA)も生まれました(図14)。

BGAパッケージでは多くのピンがパッケージ全面にアレイ状に配置されています。

多くのチップパッドからBGAのピン(ボール)への配線は非常に複雑になり、単純なリードフレームなどでは配線できなくなりました。複雑な配線では多層配線で、層を切り替え、配線を交差する必要があります。

ここで、インターポーザーに多層配線板を使う必要が出てきました。

この時点でチップの信号数は数百となり、しかもパッケージを小さくするためにはチップパッドのピッチは狭く、配線や配線切り替えのビアや信号配線をファイン化する必要があります。

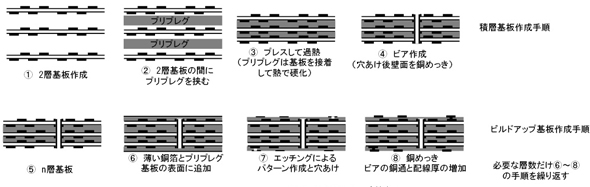

その頃、シーズとしてはちょうどビルドアップ基板の技術が開発されました(図15)。

薄くファイン化が可能なビルドアップ基板はインターポーザー基板としてよく使われています。

Copyright © ITmedia, Inc. All Rights Reserved.