MPUとの連携で存在感を強めるザイリンクスのFPGA:電子機器 イベントレポート(28)TEDプログラマブル・ソリューション 2011(1/3 ページ)

東京エレクトロン デバイスは2011年2月16日、東京都内でプライベートカンファレンス「TEDプログラマブル・ソリューション 2011」を開催。パートナ企業とともに、FPGAに関する最新の技術・ソリューションを披露した。特に目を引いた「MPUとFPGAの連携」の部分をレポートする。(編集部)

東京エレクトロン デバイス(以下、TED)は国内で唯一、世界でも数少ない米ザイリンクスの「アライアンスプログラム プレミアメンバー」に認定されている。その同社がプライベートカンファレンス「TEDプログラマブル・ソリューション 2011」において、ザイリンクス製品にまつわる最新ソリューションを一堂に披露した。「組み込み機器開発ではますます効率性、柔軟性が要求され、FPGAのニーズは高まっている」(同社)と、前年を上回る規模で催しは行われた。

「何でもありのコア」のCortex-A9

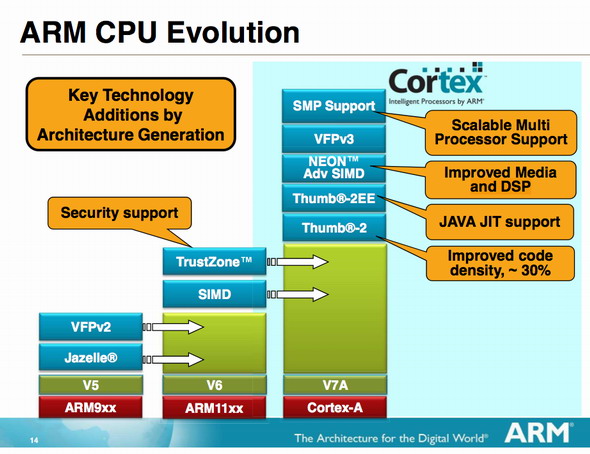

FPGA中心のカンファレンスながら基調講演に立ったのは、アームのマーケティング&ビジネス デベロプメント シニアマネージャー 平田 一行氏だった。それと言うのも、ザイリンクスの28nmFPGAでARMコアを採用したFPGAプラットフォーム「Extensible Processing Platform」が発表され、FPGA分野でもARMの存在感は高まっているのだ。

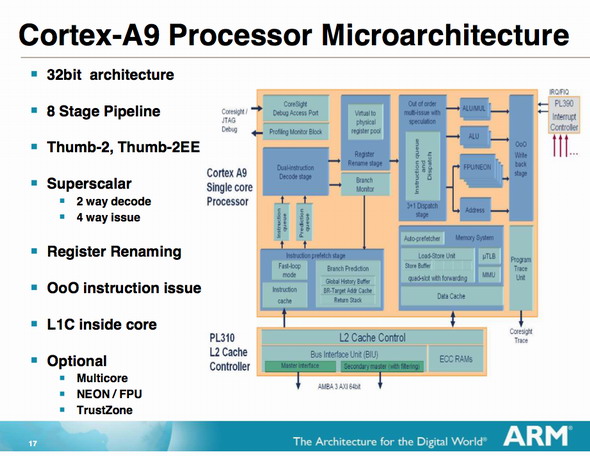

平田氏は、Extensible Processing Platformに採用されたアプリケーションプロセッサ向けCPUコア「Cortex-A9」の解説を中心に行った。Cortex-A9はアウト・オブ・オーダー(非順次処理)型で2命令同時実行、4命令同時発行のスーパースカラ構造を採用。2〜4のマルチコア化に対応しており、各コアはスヌープ制御ユニット(SCU)でキャッシュコヒーレンシが維持される仕組みだ。また、外部アクセラレータ回路は、SCUに設けられた「Accelerator Coherence Port」を介してL1/2キャッシュ(L1はコア内蔵)のデータへ直接アクセスできるため処理が早い。

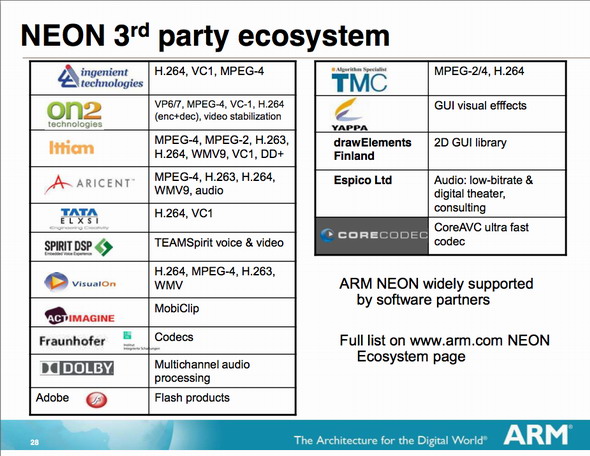

平田氏がCortex-A9で強調したのは、SIMD(Single Instruction Multiple Data)エンジン「NEON」の存在だ。コアごとにオプションで追加でき、メディア処理性能を飛躍的に高められる。エコシステムの充実も特徴だ。米Khronosが策定した業界標準のメディア処理向け低レベルAPI「OpenMAX DL」に対応し、NEONに最適化されたオープンソース、商用のコーデックも数多い。例えば、動画コーデック「Google WebM」は1万1000行がNEONアセンブラという。

実際、Android 3.0端末、ソニーの新型PSP「Next Generation Portable」、PSPとAndroidを融合させた「Xperia PLAY」など、平田氏が紹介した採用例からもCortex-A9のメディア処理能力はうかがい知れた。一方で「FPGAと相性のよいインフラ関係での採用例」として、開発中のLTO(Long Term Evolution)基地局やサーバ製品も紹介された。まさに同氏が言う通り「何でもありのコア」である。

Copyright © ITmedia, Inc. All Rights Reserved.