SPICEの過渡解析(その2):インダクタンス素子の場合:SPICEの仕組みとその活用設計(5)(3/4 ページ)

SPICEの過渡解析では、第4回で紹介したキャパシタンス素子の他に、インダクタンス素子も対象となる。第5回では、このインダクタンス素子を用いた回路の過渡解析について取り上げる。また、理想電圧源の組み込みについても説明する。

理想電圧源の組み込み

連載の第2回では、内部抵抗のある電圧源について説明しました。ここからは本記事を参考にして、内部抵抗のない、理想電源の組み込みについて考えます。

図1を見ればReq(L)=0、E=設定電圧の場合が理想電圧源の組み込みになることは明らかですので、インダクタの解析手順①〜⑥のみを実行することになります。そして、同じアルゴリズムを使うため電源に電流が流れ込む方向を正とします。

① 電圧ベクトル[V]の末尾に電源電流ieが入る

② 電流ベクトル[I]の末尾に電圧源が入る

③ g(i,m+p)=1(1列拡張し、i行に+1)

④ g(j,m+p)=−1(拡張された列のj行に−1)

⑤ g(m+p,i)=1(1行拡張してi列を+1)

⑥ g(m+p,j)=−1(拡張した行のj列を−1)

計算例

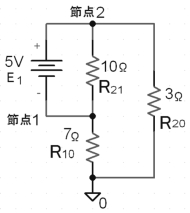

計算例として、図4の回路を考えます。

まず、電圧源E1を除いて従来の通り、回路要素行列[G]を構成します。節点番号は0〜2です。

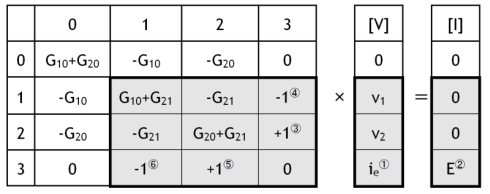

続いて、上記のルール①〜⑥を適用すると、次の表1のような拡張された行列やベクトルを得ることができます。

G10=1/7=0.1428…、G20=1/3=0.33…、G21=1/10=0.1なので、それぞれ代入して、4×4の行列を作り、0行、0列を抜いて3×3の行列(灰色部分)とすると、式(9)に示す行列になります。

式(9)の逆行列を求めて、電流ベクトル[I]に左からかければ式(10)のように、v1,v2,ieが求まります。

もちろん、手計算で計算した結果と合致しています。

ieが負になっているのは、「電圧源に電流が流れ込む」と仮定したものが、実は流入ではなく流出になっていることを示すものです。節点1の電圧v1が負になっているのは、電圧源E1がフローティングになっており、節点0(接地)から見ると負電位になっているためです。当然、節点①〜②間の電位差は5Vです。

この理想電圧源は設定電圧を0Vに設定しても動作しますので、電圧源を通過する電流を検出することができます。

つまり、設定電圧が0Vなので、電圧降下を生じない理想的な電流検出器として動作させられるのです。

SPICEが内蔵している電流制御型素子(F素子、H素子)の電流検出器にはこの機能が使われていますので覚えておいてください。

Copyright © ITmedia, Inc. All Rights Reserved.