第15回 新しいMCM(2.5D実装):前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第15回は、先端FPGAなどへの採用が始まっている、新たなMCM技術である2.5次元(2.5D)実装について説明する。

5. シングルチップからマルチチップへ

以上、システムICが巨大化するに従い、次のような問題が大きくなってきました。

- 設計の巨大化

- IC歩留まりの低下

また、SoCで多くの機能ブロックを1チップに集積しようとする動きは、大きな問題に直面しはじました。これは光素子やセンサなど、前に述べたように、IPによるテクノロジの違いです。

IPが出現してしばらくの間は、IP設計は最新のテクノロジで設計されていたので、テクノロジの差異はそれ程大きくありませんでした。しかし、テクノロジの進歩に合わせ、新しいIPは新しいIPは新しいテクノロジになりますが、用途によっては、古いIPを使う必要があります。

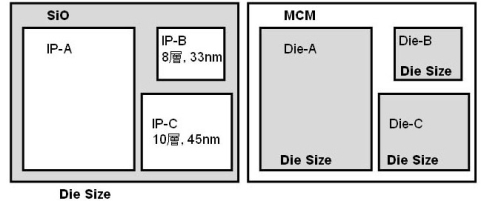

低レベルのテクノロジIPでも高度なテクノロジで製造すればよいのですが、古いテクノロジIPのため、ダイサイズが大きくなり、チップコストの上昇を招く場合があります(図11)。

できれば、ダイサイズは小さくしたいものです。

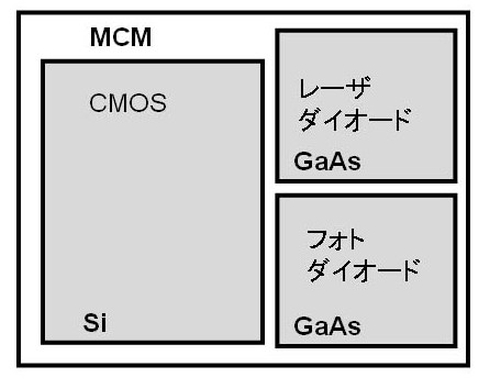

また、光ICやセンサなどはCMOSロジックICとは異なる不純物を混ぜて異なる半導体構造を作る必要があります。同一チップに場所ごとに異なるイオンを注入することは技術的にも困難ですし、コストもかかり、チップの有効使用面積も小さくなります。このように異なるテクノロジの素子を1パッケージに収める場合にMCMは有効な解決になります(図12)。

SoCが有利な点は非常に小さな1チップの中に、システムを収められることです。いくらダイサイズが大きくなってきたとはいえ、これまでの技術ではマルチチップにするよりはシングルチップの方がずっと小さくできます。

部品の小型化はIP間の接続距離を短縮し、配線による信号歪みを小さくし、回路の高速動作を可能にします。 ここで、ブレークスルー技術として、TSVを使ったシリコン基板の上に複数のダイを並べてSiP化する新しいマルチチップモジュールが浮上してきました。

大きいシリコンチップをいくつかに分割して、最小の隙間でシリコン基板(インタポーザ)の上に配置しようというのが、新しいMCMの考えです。

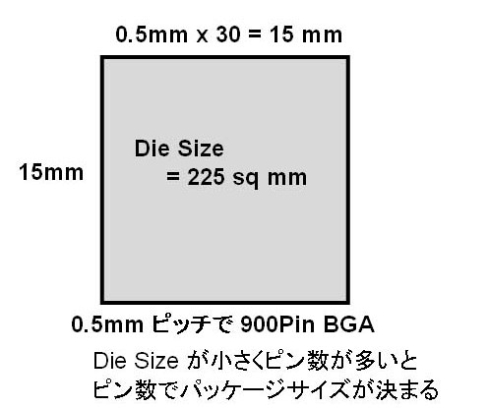

シリコンチップの配置間隔を小さくすればシングルチップのSoCとの大きさはそれほど変りません。SoCではIP間配線に使われていた領域が不要になるので、MCM化してもそれほど面積は変らなくなります。CSP(Chip Size Package)を使ってダイサイズとほぼ同じサイズのLSIを考えると、TSVを使ったシリコンインタポーザ基板MCMでもほぼ同じパッケージサイズが実現できます。

さらにパッケージのピン数が多い場合には、パッケージのサイズはダイサイズではなく、ピン数で決定されるので、MCMのパッケージサイズはSoCと変らなくすることができます(図13)。

マルチチップ化して、ダイのサイズを小さくすると、チップの歩留まりは飛躍的に向上します。また、層数の少ないチップなどを別チップにすれば、これらのチップの製造コストが安くなります。

しかし、インタポーザを介するため、ICチップとインタポーザの接続、TSVを介したインタポーザ内の配線の歩留まりと信頼性はコストの重要な問題となります。

当然、MCM化することにより、異なる組成の光素子やセンサなどを自由に組み込んだシステムが構築できます。

チップ間配線は、1チップのチップ内配線に比べ、パッドやTSVを介する必要があり、特性の劣化が予想されます。このため、インタポーザ内配線の電気特性についても大きな注目がされています。

設計、開発期間とコストについてはMCMの方に大きなアドバンテージがあります。

皆さんも、標準部品を集めて基板でシステムを構築する方が標準IPを集めてASICを起すよりずっと開発期間も設計コストが安いことはごぞんじでしょう。

ICは試作チップを作成して、それと同時に動作確認用基板を作成し、で動作を確認後、手直しを行うためのTAT(Turn Around Time)が非常に長く、コストもかかります。

このため、ASICを開発するためには、必ず基板でシステムを構築して、試作基板で動作を確認する手法が良く取られます。

MCMに使うシリコンインタポーザはこの基板に相当します。基板システムの開発と同じMCM開発はSoC開発より、ずっと早く安くシステムが開発できます。

面白いことには、発表などを見る限り、このMCM開発では、ASICベンダよりもFPGAベンダのほうが現在は先行しているように見えます。

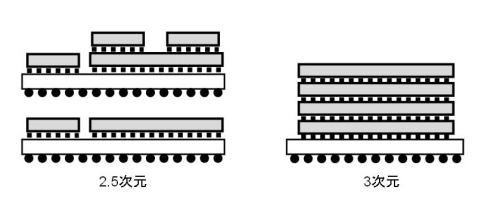

現在、このようなTSVを使用したシリコンインタポーザの上にICチップを配置してSiPを作成する設計を2.5次元(2.5D)実装と呼んでいます。

同じTSVを使用してもメモリチップなどのチップのスタック実装の3D実装とは区別しています(図14)。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫前田真一の最新実装技術あれこれ塾

- 第3回 TSVがもたらす新しいMCM

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第3回は、パッケージ内でメモリチップを積層するためのキーテクノロジとして注目されている「TSV」について紹介する。