第3回 TSVがもたらす新しいMCM:前田真一の最新実装技術あれこれ塾(1/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第3回は、パッケージ内でメモリチップを積層するためのキーテクノロジとして注目されている「TSV」について紹介する。

本連載は「エレクトロニクス実装技術」2011年6月号の記事を転載しています。

1. チップの3次元実装

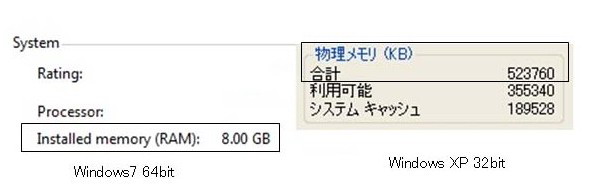

新しいMPUはこれまでの32ビットから64ビットのサポートをするようになってきています。Windows7では、32ビット版と64ビット版が用意されています。

32ビットと64ビットの違いはいろいろありますが、大きな違いの1つにメモリ容量の制限があります。32ビットでは、最大4GBまでしか数が数えられないので、メモリやディスクの容量は最大4GBが限界となります(図1)。

速度も遅く、IOコントロールの必要なディスクなどでは、パーティションを切ることにより、大きな容量をアクセスすることもできますが、できるだけ高速性を要求されるメインメモリでは、一般の32ビットPCでは4GBや場合によっては、2GBが限界となっています。

しかし、64ビットPCではこの限界がないので、物理的なアドレスピンの数によって、32GBや64GBのメインメモリが使えます。物理的なアドレスビットのピン数を増やせば、TB単位のメモリアクセスも可能です。

しかし、メモリチップの容量は簡単には増えません。

特に数年後のメモリの主流になるであろうDDR4では、DIMMの数を現在のDDR3が2つなのに比べ、1つにしなければならないのではないかとの議論すらあります。DIMM(図2)が半分になれば、単純にメモリ容量は半分になってしまいます。

このため、DDR4ではDIM内のメモリをスタック実装して、DIM1枚当りの容量を一挙に2〜8倍に増やす考えが多く出ています。

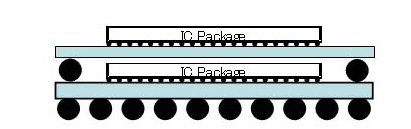

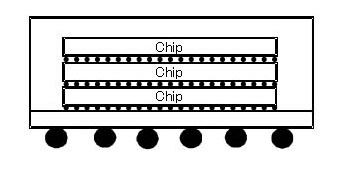

スタック実装はパッケージングしたメモリICを積層実装するPoP(Package on Package)方式(図3)で行う方法と、パッケージ内でメモリチップを積層するスタックドCSP方式(図4)が考えられます。

技術的にはPoPが簡単ですが、コストやDIMの厚さなどからは、スタックドCSPが今後のメモリの方向となると考えられています。DIMを使わず、DDRメモリを直接実装するデジタル家電などでは、スタックドCSPは1つの大容量メモリICとして扱え、現在のメモリICとまったく同様に扱えます。パッケージ内でメモリチップを積層するためのキーテクノロジとしてTSV(Through Silicon Via)が注目されています。

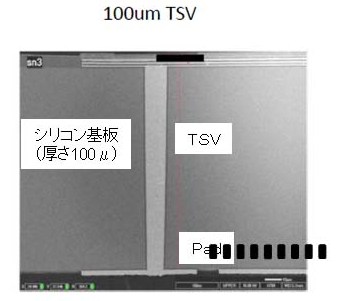

TSVとはその名の通り、シリコン(ICチップ)に開けたスルーホールビアです(図5)。ICチップにスルーホールビアを空けることにより、積層して実装した上のチップにも簡単に信号や電源を接続することができるようになります(図6)。

メモリは同じチップの積層なので、信号の種類やピン配置がまったく同じであるため、積層化が比較的簡単にできます。また使われる量も多いため、DDRメモリはチップの3次元実装普及の最もよいスタートとなると見られています。

Copyright © ITmedia, Inc. All Rights Reserved.