第15回 新しいMCM(2.5D実装):前田真一の最新実装技術あれこれ塾(2/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第15回は、先端FPGAなどへの採用が始まっている、新たなMCM技術である2.5次元(2.5D)実装について説明する。

3. SoC

システムを一つのIC部品に集積させる動向はICの集積度の向上に伴い、ずっと続いています。

CPUでいえば、PCを校正するには、当初はCPUチップの他にNorth BridgeやSouth Bridgeと呼ばれる、周辺コントローラICが別チップでありました。これらはまとめてチップセットと呼ばれていましたが、ICの集積度の向上に従い、これらはすべてCPUチップに統合されつつあります。

また、グラフィックプロセッサ(GPU)も一般的なものは、CPUに統合されつつあります。

CPUは汎用品であり、標準的な構成がありますが、ASICは特定用途、特定顧客向けのため、CPUなどに比べると小数多品種生産となり、用途ごと、顧客ごとにおのおのシステム設計をする必要があります。

ICの集積度が大きくなり、1チップに集積されるシステムの規模が大きくなるに従い、このASICの設計コストが莫大なものとなってきました。

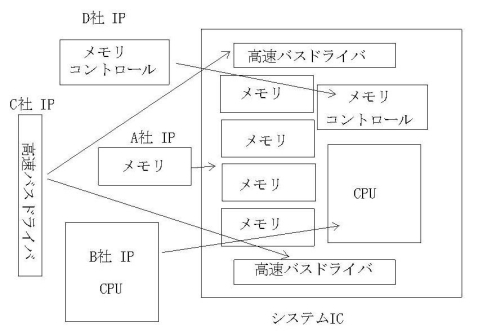

この膨大な設計時間を短縮するためにあらかじめ設計したICの機能ブロックをIP(Intellectual Property)として再利用するようになりました。現在では、各社が設計した回路ブロックが、このIPとして、流通しています(図8)。

ASICベンダはシステムに応じて、これら、自社開発、他社開発のIPを組み合わせてシステムを設計します。

また、GPUチップやビデオプロセッサなど汎用ICベンダも、実はこれらのIPを使って、製品化しています。

AppleのiPadやiPhoneをはじめ、多くの携帯機器で使われ有名なARMのCPUもIPで流通しており、各社がこのIPを購入して、自社のICに組み込んでいるものです。

また、ユーザー自身が回路を組むFPGAでも最近は多くのIP回路が組み込まれるようになっています。例えば、ARMのCPU、DDRメモリなどが、FPGAに組み込まれるようになってきました。

しかし、このようなIPを使う設計でも、LSIの大規模化やシステムの巨大化はSoCにとって大きな問題となっています。特にシステムの巨大化が大きな問題となっています。

4. システムの巨大化とSoC

ICの集積度の向上は、基本的にはIC配線の微細化で実現されています。論理素子やメモリを作る回路が簡単になり、同じ回路を実現するためのトランジスタ数が減ったわけではなく、トランジスタが小さくなったためにICの集積度が向上しているのです。

それどころか、回路の設計が高レベル言語を使ったり、以前の回路のライブラリや他のIPの利用したりすることにより、同じ回路を実現するためには以前よりは多くのトランジスタを使用するようになっています。つまり、ゲートの使用効率は下がってきているのです。これはシステムが巨大化するに従い、開発に多くの時間が掛かるようになり、ゲートの使用効率よりも回路の開発効率を重視するための結果です。

システムの巨大化は設計コストの大幅な上昇につながります。巨大化するシステム設計の効率化のためにIPを導入するようになりましたが、それでも開発は複雑さを増し、開発期間は長くなってきます。

例えば、IP単体では動作検証され、レイアウトも安定しているとしても多くのIPを接続したシステムではIP巻の接続に対しての設計、検証が残っています。多くのIPを接続した検証では、膨大な時間とリソースが必要となります。

当初、日本の多くのICベンダがシステムICビジネスの拡大に期待していましたが、最近では、システムIC部門の赤字や合併、規模縮小などのニュースばかりが目立つようになってきました。この裏にはシステムの巨大化による開発コストの上昇が大きな理由としてあります。

回路の微細化速度以上にシステムの巨大化が進んだ結果、LSIのダイのサイズが巨大化する傾向があります。

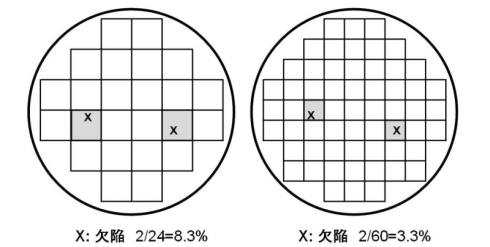

微細配線ダイの巨大化はLSIの歩留まりの悪化と、高価格化の原因となります(図9)。

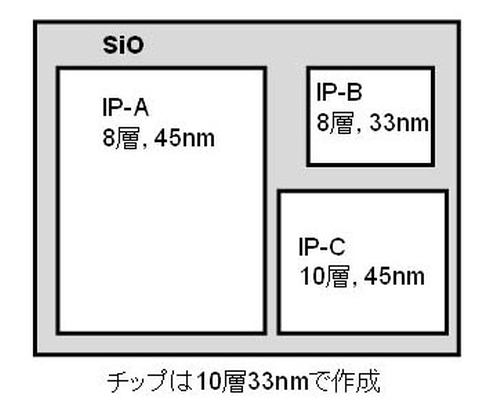

実はシステムASICで使用するレイアウトIPでは、IPごとに必要な配線幅や層数が異なります。しかし、複数の設計IPを集積するシステムICでは、これらIPのなかで最小幅テクノロジーを使い、最大層数のチップにすべてのIPを組み込む必要があります(図10)。

Copyright © ITmedia, Inc. All Rights Reserved.