第13回 TSVが量産技術へ〜Wide I/O規格:前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第13回は、JEDECが2011年末に規格内容を正式に発表した、次世代メモリインタフェース「Wide I/O」について説明する。

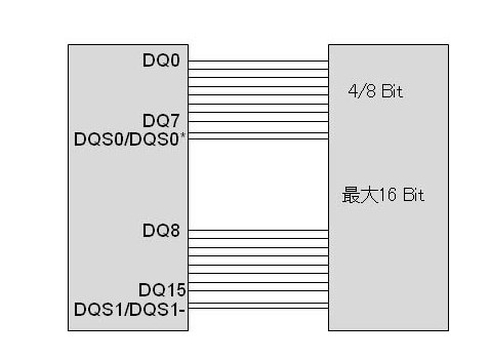

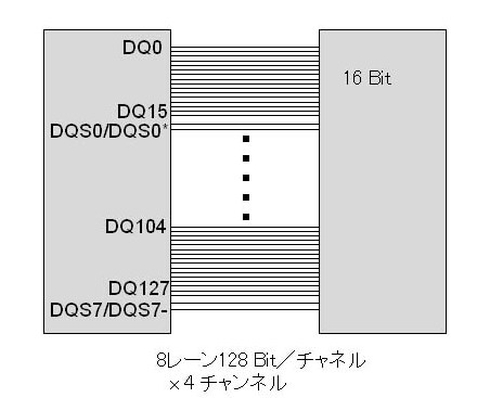

これまでのLPDDR2やDDR3などJEDEC規格のメモリバスでは並列して一度送るデータ(DQn)は4ビット、または8ビット単位です。この4ビットまたは8ビットごとに同期信号(DQS/DQS-)を同時に送り、同期させています。この4ビットや8ビットの信号群(レーン)を複数、同時に送ることにより、8ビットから32ビットの並列データをやり取りしています(図9)。

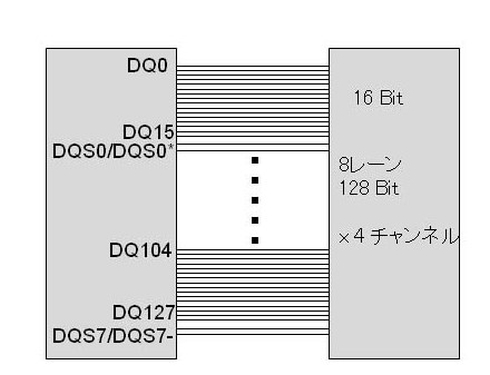

Wide I/Oメモリでは1つの同期信号に同期するデータが16ビットとこれまでの倍になっています。この16ビットのデータブロック(レーン)をチャネルあたり8組、並列にして128ビットのデータを同時に送ります。

この同一内1ビットのデータ同期はもちろんですが、8つのレーン間の同期誤差(スキュー)についても一定の値以下にする必要があります(図10)。

このため、Wide I/Oメモリではレーン間の同期を調整する機能が用意されています。

基本的には、データバス速度が200Mbps、今後の高速使用でも266Mbpsと遅くなったため、タイミング設計は余裕のあるものとなっています。

データバス速度が遅くなると、メモリの消費電力が大幅に減少します。

図6の回路で、負荷Cが増大すると信号の速度が遅くなると説明しました。

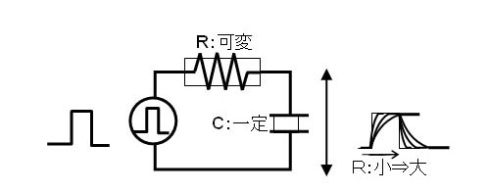

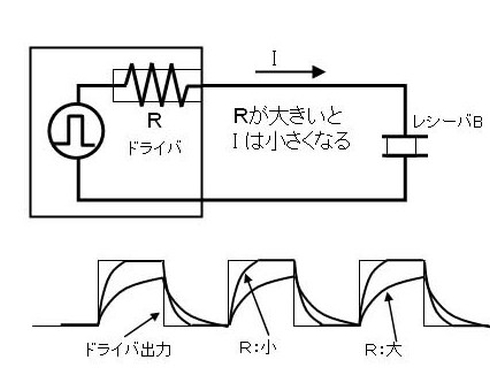

この積分回路はCの変化だけではなく、ドライバのもつ出力インピーダンス(R)によっても波形が変化します。Rを小さくすると波形は早い立ち上がり/立ち下がりとなり高速動作が可能となります(図11)。しかし、Rが小さくなると回路に流れる信号電流が大きくなり、回路の消費電力が増大し、消費電力が増大します。信号速度が遅くなれば、ドライバのRを大きくし、信号電流を減少させることができます(図12)。

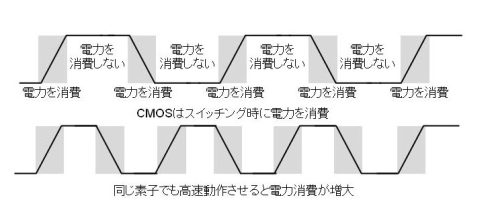

また、CMOS回路では信号が変化している時に大きな電流が流れるので、回路が低速化して、信号が安定している時間が長くなれば、消費電力が減少します(図13)。

Wide I/OメモリではTSVを使い、配線長さを極限まで短くしています。

信号の波長に比べ、配線が短いため、メモリパッケージ内のメモリとコントローラ間の配線は伝送線路としてみる必要がありません。このため、信号の電力を小さくしてデータ転送が可能となります。

このようにWide I/Oメモリはこれまでのメモリに対して大幅な消費電力の削減が期待されています。しかし、Wide I/Oメモリでは512ビットという多くのデータが同じタイミングでスイッチングをおこないます(図14)。

このため、大きな同時スイッチングノイズが発生する危険性があります。この同時スイッチングノイズ対策として、Wide I/Oメモリでは多くの電源・グランドピンを用意します。

DDR2メモリではIO電源ピンが大容量タイプでも8本、IOグランドピンが8本ですが、Wide I/Oメモリではおのおの64(チャネルあたり16)本が用意されています。

また、パッケージ内でのメモリチップ間接続の方法にはL成分が大きく同時スイッチングノイズが発生しやすいワイヤボンディングではなく、TSVの使用が期待されています。

5. System ICも対応が必要

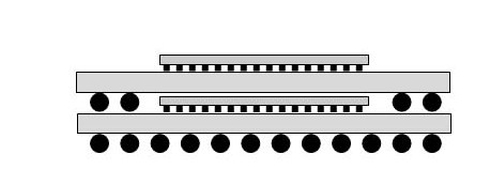

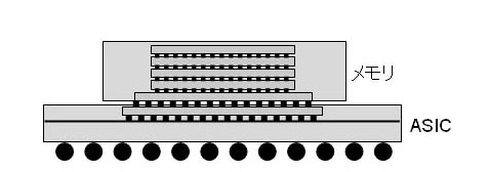

モバイル用メモリを使う製品では、製品の小ささ、薄さ、軽さが大きな性能要素になります。このため、部品をできるだけ小さくするために、PoP(Package on Package)実装やSoS(Silicon on Silicon)実装が多く使われます(図15)。

LPDDR2メモリのパッケージは0.4〜0.65 mmピッチで89〜240ボール(パッド)です。これに対して、Wide I/Oメモリでは、40μm×50μmピッチで1200パッドとなります。

これを実装するためにはコントローラIC側にも同じだけのパッドを配置、配線する必要があります(図16)。これだけの多ピンをファインピッチで接続するためにはコントローラIC側の設計、高信頼性接続技術が要求されます。

システムICサイドでもWide I/Oメモリ対応技術が発表され始めています。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第3回 TSVがもたらす新しいMCM

第3回 TSVがもたらす新しいMCM

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第3回は、パッケージ内でメモリチップを積層するためのキーテクノロジとして注目されている「TSV」について紹介する。 第9回 TSVを前提としたモバイルDDR

第9回 TSVを前提としたモバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第9回は、モバイルDDRメモリの最新規格である、LPDDR3と、第3回で取り上げたTSVによって実現可能になったWide IOについて解説します。