RC回路を使って最も簡単にFPGAにセンサーを接続する方法:注目デバイスで組み込み開発をアップグレード(23)(3/3 ページ)

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。今回は、RC回路を用いることで、FPGAに簡単にセンサーを接続する方法を紹介する。

計測してみよう

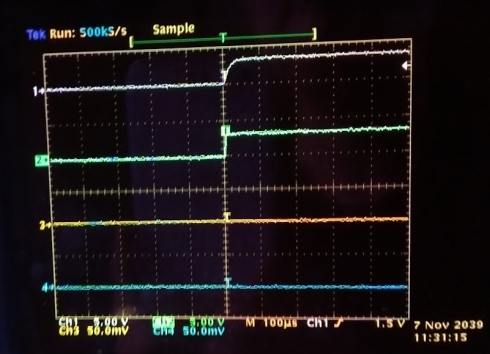

図5は、VinとVcを観測した波形です。Ch2がVinでCh1がVcになります。光センサーに当たっている光の明るさは、筆者が原稿を執筆している部屋で利用しているLEDスタンドの明かりです。Vinの立ち上がりから徐々にVcの電圧が上昇していく様子が分かります。

図6は、光センサーにLEDライトの光を直接当てた時の波形です。Vinの立ち上がりに対して、図5よりもかなり急激にVcの電圧が上昇しています。これは光センサーの抵抗値が低くなったことを示しています。

この時間差を観測することで、光センサーに当たる照度の違いを捉えようというわけです。

FPGAに組み込むプラグラムコード

ここからはFPGAに組み込むプラグラムコード(rcSensor.v)と物理制約ファイル(rcSensor.cst)を紹介します。以下のGitHubのリポジトリからソースコードを入手できます。

⇒rcSensor.vとrcSensor.cstのあるGitHubのリポジトリはこちら

リスト1に示すrcSensor.vは、Vinの立ち上がりからVcがFPGAで1と判断されるしきい値の電圧に達するまでの時間を計測するVerilog-HDLのプログラムコードです。

8行目でカウントした時間が、計測結果としてRegs[7]に代入され、LEDドットマトリクスの一番下に表示されます。左端が最下位ビット、右端が最上位ビットになります。

1: module rcSensor(input clk,Vc,output [7:0]col,[7:0]row, Vin); 2: reg [7:0]regs[7:0]; 3: reg [18:0] counter; 4: assign col = regs[counter[15:13]] ; 5: assign row = ~(1<<counter[15:13]); 6: assign Vin = counter[18]; 7: always @(posedge clk) counter <= counter + 1; 8: always @(posedge Vc) regs[7]=counter[17:10]; 9:endmodule

リスト2のrcSensor.cstは、VerilogHDLコードで記述されている入出力の信号線を実際のFPGAのピンに割り当てるための物理制約ファイルです。冒頭の4行で、VinとVcに関する設定を行っています。

IO_LOC "clk" 52; IO_LOC "Vin" 53; IO_PORT "Vin" PULL_MODE=DOWN; IO_LOC "Vc" 69; IO_LOC "col[0]" 74; IO_LOC "col[1]" 34; IO_LOC "col[2]" 40; IO_LOC "col[3]" 71; IO_LOC "col[4]" 41; IO_LOC "col[5]" 72; IO_LOC "col[6]" 76; IO_LOC "col[7]" 77; IO_LOC "row[0]" 70; IO_LOC "row[1]" 75; IO_LOC "row[2]" 51; IO_LOC "row[3]" 73; IO_LOC "row[4]" 30; IO_LOC "row[5]" 42; IO_LOC "row[6]" 33; IO_LOC "row[7]" 35;

センサー値の実測

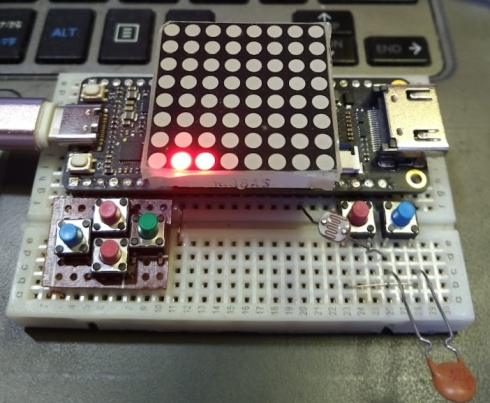

記事の冒頭に掲載した図1は、FPGAに光センサーとコンデンサーから成るRC回路をつなげて、リスト1のコードによってセンサー値の実測を行っている様子です。

LEDマトリックスの一番下の行に表示されているのがregs[7]の値です。左から2番目の2の位と3番目の4の位が点灯しているので、10進法では6になります。すなわち、Vinに電圧を印加してVcがしきい値に達するまでに6カウントを要しました。周囲を暗くするとこの値は大きくなり、明るくするとこの値は小さくなります。

見えてきた課題

センサーの抵抗値が大きくなりすぎると、VinをGNDに落としてもコンデンサーCの静電容量で完全に受けきれず、Vcの値が高止まりしてしまいます。こうなると常にVcはしきい値を超えた状態になり測定ができなくなります。

測定可能範囲をセンサーの抵抗値がある程度小さい範囲に限定するか、もう一つオープンドレインなどの出力ピンを用意してコンデンサーCの静電容量を短時間に抜くなどの対策が必要かもしれません。

おわりに

HDLコードに関してあまり突っ込んだ話はしませんが、今回分かっていただきたいのは、抵抗値が変化するセンサーであれば、コンデンサーが1個あればFPGAでセンサー値を取得できるということです。しかもコードの行数は10行足らずです。

今回は、とにかく原理をお伝えしたかったので最も簡単に確認できる方法を紹介しましたがお楽しみいただけたでしょうか。また、次回お会いしましょう。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

FPGA評価ボードに十字キーを付けてみた【後編】

FPGA評価ボードに十字キーを付けてみた【後編】

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。第19回では、前回作成したFPGA評価ボード「Tang Nano 9K」とつなげた十字キーとA/BボタンのUIによる「お絵描きソフト」を紹介する。 FPGA評価ボードに十字キーを付けてみた【前編】

FPGA評価ボードに十字キーを付けてみた【前編】

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。第18回では、筆者の今岡氏が他連載でも活用しているFPGA評価ボード「Tang Nano 9K」に、ファミコンで広く知られるようになった十字キーとA/BボタンのUIを搭載する。 加湿器トランスデューサの水中通信実験で「ロバチャン」が進化する【後編】

加湿器トランスデューサの水中通信実験で「ロバチャン」が進化する【後編】

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。今回は、連載第21回で紹介したコンテスト「ロバチャン」の進化に向けて行った、加湿器のトランスデューサを用いた水中通信実験の構想と結果について紹介する。 加湿器トランスデューサの水中通信実験で「ロバチャン」が進化する【前編】

加湿器トランスデューサの水中通信実験で「ロバチャン」が進化する【前編】

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。第21回と第22回では、筆者が設計に関わったコンテスト「ロバチャン」を紹介するとともに、その進化に向けて行っている加湿器のトランスデューサを用いた水中通信実験について解説する。 FPGAでミュージックシーケンサーを作る

FPGAでミュージックシーケンサーを作る

注目デバイスの活用で組み込み開発の幅を広げることが狙いの本連載。第20回は、筆者が独断と妄想に駆られて作ってみたFPGAで制御するミュージックシーケンサーを紹介する。