インテルがガラス基板で半導体進化の限界を打ち破る、2020年代後半に量産適用:材料技術(1/2 ページ)

インテルは、複数のチップレットを搭載する大規模半導体パッケージの進化に貢献するガラス基板技術の開発を進めるとともに、10億米ドル以上を投資して研究開発ラインを構築したことを明らかにした。

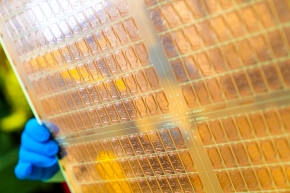

インテル(Intel)は2023年9月18日(現地時間)、データセンターやAI(人工知能)処理などに用いられる複数のチップレットを搭載する大規模半導体パッケージの進化に貢献するガラス基板技術の開発を進めているとともに、10億米ドル以上を投資してチャンドラー工場(米国アリゾナ州)にガラス基板を用いた半導体パッケージの研究開発ラインを構築したことを明らかにした。今後は2020年代後半の実用化に向けて開発を進め、2030年に1個の半導体パッケージ内に1兆のトランジスタを集積するという同社の目標の実現に活用する計画である。

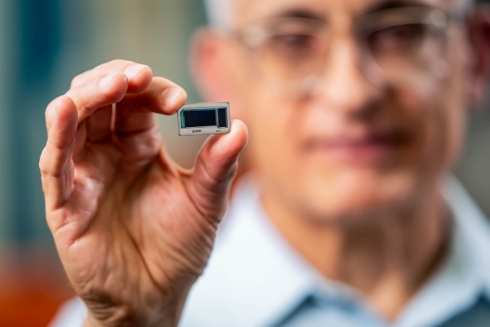

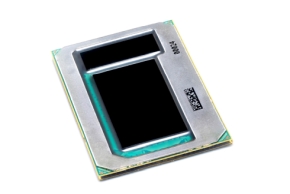

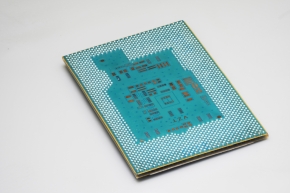

ガラス基板の試作パッケージの表面(左)と裏面(右)。表面にはチップレットが2個搭載されており、回路基板に接合する側となる裏面はBGA(Ball Grid Array)となっている[クリックで拡大] 出所:インテル

ガラス基板の試作パッケージの表面(左)と裏面(右)。表面にはチップレットが2個搭載されており、回路基板に接合する側となる裏面はBGA(Ball Grid Array)となっている[クリックで拡大] 出所:インテル3nmプロセスでの半導体量産が始まる中で、これまで半導体の微細化をけん引してきたムーアの法則が限界を迎えつつあるといわれている。実際に、半導体ウエハーから切り出した1個当たりのシリコンダイでみると、最近では2年ごとにトランジスタの集積度が2倍になるというムーアの法則を実現できなくなりつつある。その一方で、多機能のシリコンダイであるチップレットを積層するなどの半導体パッケージ技術の進化が、ムーアの法則を維持する上で大きく役立っている。

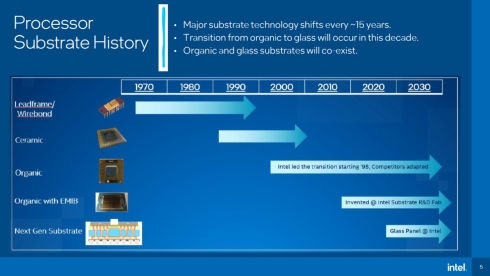

今後もさらなる半導体パッケージ技術の進化が求められるが、ボトルネックとして指摘されていたのがパッケージ基板である。これまでも、半導体パッケージ基板は、1970年代に用いられていたリードフレーム/ワイヤボンドから、セラミック基板、有機基板、そして現在のシリコンインターポーザーを搭載した有機基板といった形で約15年ごとに進化してきた。しかし、より高い処理性能が求められる生成AIなどに対応するため、さらに多くのチップレットを基板上に搭載することが難しくなりつつある。

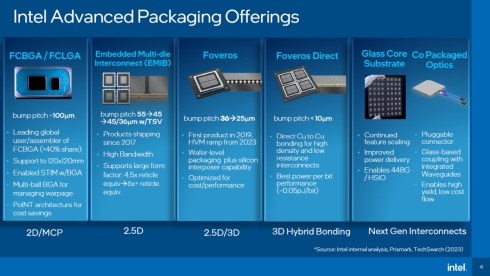

インテルも、2.5次元パッケージング技術の「EMIB(embedded multi-die interconnect bridge)」や、3次元パッケージング技術の「Foveros」「Foveros Direct」などを開発しているものの、2030年以降を見据えたブレークスルーが必要になっていた。このブレークスルーこそが、基板材料を有機基板からガラス基板に置き換えることだ。

Copyright © ITmedia, Inc. All Rights Reserved.