2nm半導体プロセスの開発は順調、ナノシートトランジスタの完成度は80%以上:材料技術(1/2 ページ)

TSMCは、横浜市の会場で会見を開き、量産に向け開発を進める2nm世代半導体プロセス「N2」の開発が順調だと明かした他、N2で構築されるナノシートトランジスタの技術完成度は目標の80%以上を達成していると発表した。

TSMCは2023年6月30日、横浜市の会場で、半導体テクノロジーに関する説明会を開き、同社の半導体プロセス技術や日本国内での取り組みなどを紹介した。

N2のオプションとしてバックサイドパワーレールを2025年後半に発売

同社は2018年に7nm世代半導体プロセス「N7」の量産を開始したことを皮切りに、1桁nmレベルの微細化を実現したロジックICであるハイエンドナノサイズロジックデバイスの提供を開始した。2020年に量産を開始した5nm世代半導体プロセス「N5」については、同社がナノサイズロジックデバイスのプロセス開発を積み重ねる中で培ったノウハウを反映することで、開発当初と比べて現行のN5プロセスは性能が17%向上し、チップ密度も6%アップしているという。さらに、既存の回路設計データを最大限に再利用できるように現行のN5プロセスのデザインルールは開発当初との互換性も確保している。

2022年第4四半期(10〜12月)にはには3nm世代半導体プロセス「N3」による量産をスタートした。N3の派生プロセスとして、2023年後半に「N3E」を、2024年後半に「N3P」を、2025年に「N3X」を量産を開始する他、車載用として2024年に「N3AE(3nm Auto Early技術)」を、2026年に「N3A」の量産を始める予定だ。

N3Eは、既に技術認定に合格し、性能と歩留まりの目標を達成している。加えて、現行のN5プロセスと比較して、同じ消費電力で18%の処理速度向上を実現し、同じ処理速度で32%の消費電力を削減しているだけでなく、約1.6倍のロジック密度と約1.3倍のチップ密度を実現している。

N3Pは、回路設計データの再利用を最大化するために、N3Eと互換性があるデザインルールを採用し、N3Eと比べ、同じリーク電流で処理速度を5%向上し、同じ処理速度で消費電力を5〜10%削減しており、チップ密度が1.04倍アップしている。

N3Xは、ハイパフォーマンスコンピューティング(HPC)向けに調整されており、リーク電流とのトレードオフを抑えつつ、オーバードライブ性能を高めるために、最高発振周波数(Fmax)のゲイン(電気回路の増幅器で電気信号を増幅すること)を追加している。これにより、駆動電圧1.2Vの場合、N3Pと同じチップ密度で、N3Pより処理速度は5%高速化されている。

N3AEは、N3Eをベースとした車載用プロセスデザインキット(PDK)を提供し、3nmノードで顧客が車載向けアプリケーションを構築できるようにする。N3Aはそのプロセスが2025年に自動車製造プロセスの認証を全面的に受けた後、提供を開始する見込みだ。

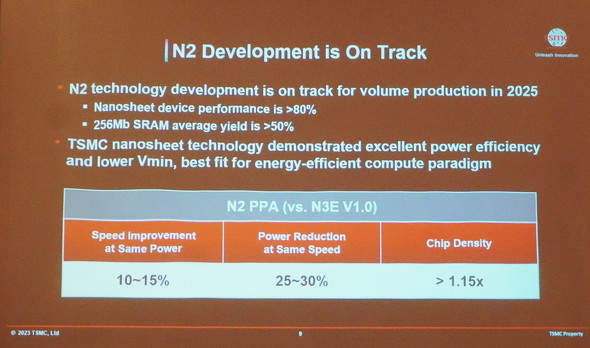

次世代のロジックデバイステクノロジーとして注目されている2nm世代半導体プロセス「N2」の量産は2025年を目標としている。TSMC Business Development シニア・バイスプレジデント Dr.Kevin Zhang(ケビン・ジャン)氏は、「N2は、ゲート絶縁膜をシリコンのナノシートに巻き付けた『Gate All Around(GAA)』を適用したナノシートトランジスタのプロセスで、2025年の量産に向け開発は順調だ。N2で構築されるナノシートトランジスタの技術完成度は目標の80%以上を達成しており、優れた電力効率と低い最小電源電圧(Vmin)を実証している」と話す。

N2のオプションとしてバックサイドパワーレールを2025年後半に発売する。バックサイドパワーレールは、材料を通る電子の流れに起因する過電圧(IRドロップ)とRC遅延(配線抵抗や配線間容量/層間容量の影響で入力から駆動までの時間が遅れること)の低減により電力の供給速度を10〜12%高める。さらに、半導体基板の表側の配線リソースを増加可能なため、ロジックICの面積を10〜15%減らせる。HPC向けにN2を採用する場合に適しており、基礎の配線網と併用することで、処理の高速化と配線の高密度化も実現できる。

ジャン氏は「バックサイドパワーレールについては、開発中のため詳しいことは説明できないが、シリコンダイの裏面側に電源供給配線網(PDN)を設ける『バックサイドPDN』に相当するものだと考えている」と話す。

Copyright © ITmedia, Inc. All Rights Reserved.