ヘテロジニアスデザインと先進的パッケージングがPPACtを改善:アプライド マテリアルズ ブログ(1/2 ページ)

米国の大手半導体製造装置メーカーであるアプライド マテリアルズ(Applied Materials)のブログの抄訳を紹介する本連載。今回は、同社のMaster Classイベントで発表されたヘテロジニアスデザインと先進のパッケージング技術について紹介する。

本記事は「Applied Materials Blog」の抄訳です。

私の同僚Mike Chudzikが書いた前回のブログ記事に続き、私は9月8日に開催されたMaster Classイベントにおける第2のテーマ、すなわちヘテロジニアスデザインと先進のパッケージング技術について述べてみようと思う。

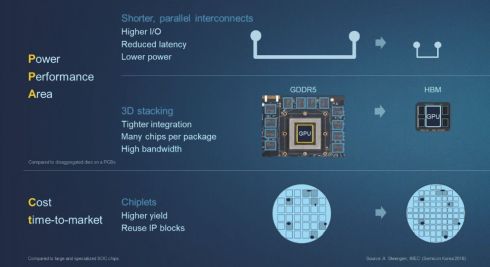

過去数十年にわたり、PPAC(消費電力、性能、面積、コスト)の同時改善は、2次元の微細化と半導体のモノリシックIC化によって着実にもたらされてきた。しかし、ムーアの法則に沿ったこの古典的な2Dスケーリングは減速しており、費用もかさんでいる。そこで半導体メーカーの間では、ヘテロジニアスデザインとパッケージング技術を用いてチップレットやデバイスをパッケージ上にインテグレートする動きが活発化している。その狙いは、PPACに市場投入までの期間(t)を加えたPPACtを加速して改善することにある。こうした動きを支える最近のデザイントレンドと、パッケージングのロードマップが示す方向性について考える。

ヘテロジニアスデザインの台頭

これまで半導体パッケージングの主な機能は、ダイを保護すること、そしてこれをプリント基板(PCB)に接続することだった。そのため、パッケージングは業界内では価値の低いコモディティ分野と見なされがちだった。しかも、チップとモジュール間に電力や信号を配信する重要な役割を担うのは、パッケージングではなくPCBだった。しかし、コンピューティングの主役がPCからモバイル機器へ、さらにはAI(人工知能)へと移行する中で、設計者のアプローチにも変化が生まれ、チップとシステムの両方を最も効率的に集積化する方法の見直しが進んでいる。ヘテロジニアスデザインと先進的パッケージング技術は、今や世界の大手半導体メーカーやシステム設計会社にとって競争力維持に欠くことのできない要素なのだ。

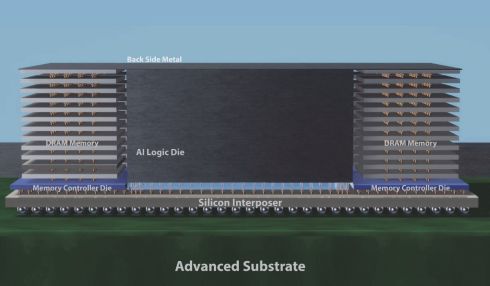

この進化を一段と促すのが、データ量が爆発的に増加しているのに対してムーアの法則に沿った古典的なスケーリングが鈍化していることだ。これまでのように、トランジスタの密度や処理速度、面積あたりコストが大幅に改善することは期待できない。その結果、ハイパフォーマンスコンピューティングや機械学習、推論といった機能に必要なトランジスタ全てを単一のダイ上に集積するのは、半導体の設計上極めて困難となりつつある。その代替アプローチとしてシステム設計者が検討を進めているのが、個別にパッケージングされたダイをPCB上に配置する代わりに、複数ダイの先進的パッケージングを通じて高性能のロジックやメモリをより密に配置し、遅延や電力消費を低減する、という方法だ。パッケージングはもはや単なる保護目的ではなく、PPACt改善の担い手となっている。

PPACtの“PPA”を改善

PCB上にチップを搭載する従来の手法に比べ、先進のパッケージング技術ではI/O密度が大幅に増加し、遅延と消費電力は大きく減少する。はんだバンプを介してチップをPCBに接続する方式に比べ、現行のシリコン貫通電極(TSV)を用いた場合のI/O密度は約100倍、1ビットのデータ伝送に必要なエネルギーは約15分の1となる(ただし数字はアーキテクチャと負荷に応じて上下する)。

先進的パッケージング技術で次に期待を集める技術革新はハイブリッドボンディングと呼ばれるもので、チップとウエハーを直接銅(Cu)配線で接続することでインターポーザーが不要となる。ハイブリッドボンディングではTSVに比べてI/O密度がさらに10倍になり、ビット当たりのデータ伝送エネルギーはTSVの2分の1になると見られている。

さらにPPACtの“Ct”も改善

ヘテロジニアスデザインは、コスト低減と市場投入までの期間短縮にもつながる。モノリシックICのアプローチではダイが極めて大型化する恐れがあり、設計からデバッグ、テープアウト(マスクデータ完成)までにかかる費用も大きい。これに対し、ヘテロジニアスなアプローチではデザインをより小さなチップレットに分割し、後でこれを単一の高性能パッケージに接続することができる。一般にダイが小さいほど歩留まりは高く、コストは低い。また、最新ノードのウエハーは旧ノードのウエハーに比べて高価な場合が多いので、性能が重視されるダイにのみこれを用い、より安価なウエハーを使ったその他のチップレットと組み合わせることにより、全体のコストを引き下げることができる。さらに、実証済みの回路情報(IP)に基づくチップレットならより短期間で組み込むことが可能だ。こうした組み合わせ(ミックスアンドマッチ)の柔軟性が、市場投入のスピードアップをもたらす。

Copyright © ITmedia, Inc. All Rights Reserved.