日立がシリコン量子ビットの開発に向け前進、超伝導量子ビットを超えるか:量子コンピュータ(2/3 ページ)

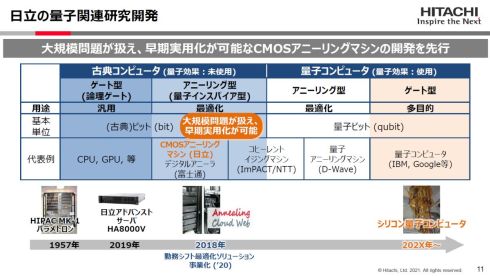

日立製作所(以下、日立)が同社の量子コンピューティング技術について説明。古典コンピュータを用いてアニーリング型の量子コンピューティングを行う「CMOSアニーリング」は事業化の段階に入っている。米中で研究開発が進むゲート型についても、シリコン半導体技術をベースとする「シリコン量子ビット」の開発で一定の成果を得ているという。

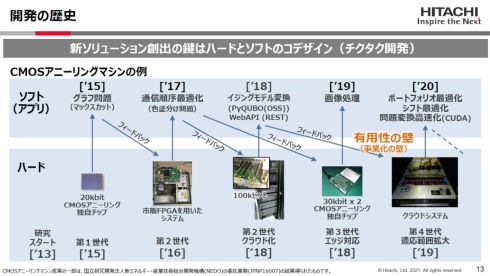

CMOSアニーリングの有用性の壁を「チクタク開発」で超える

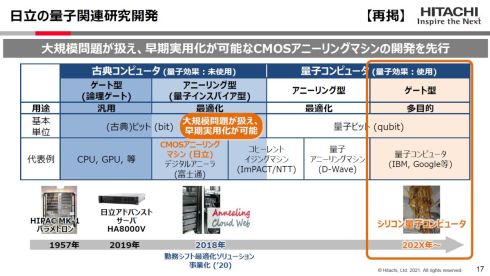

日立は、アニーリング型の量子コンピュータの実用化で世界に大きなインパクトを与えた2011年のD-Wave Systemsの発表を受け、大規模問題を扱えるとともに早期実用化が可能な古典コンピュータを用いるCMOSアニーリングの研究開発を2013年にスタートさせた。CMOSアニーリングは、量子コンピュータを使っていないこともあり「量子インスパイア型」と定義している。

2015年には、ハードウェアとして第1世代となる20kビットのCMOSアニーリング独自チップを開発。2016年には第2世代に当たる市販FPGAシステムを用いたシステムを構築し、2018年には第2世代システムをクラウド化した。2018年には第3世代となるエッジ対応も可能な30kビット×2のCMOSアニーリング独自チップを開発し、2019年には第4世代となるクラウドシステムとして適用範囲を拡大している。そして、水野氏がCMOSアニーリングの研究開発で重視してきたのが、これらのハードウェア開発とソフトウェアやアプリケーションの開発を並行して進める「チクタク開発」だ。「新たなソリューションを創出するには、ハードウェアとソフトウェアそれぞれの開発成果を互いにフィードバックして前に進めなければならない」(同氏)。

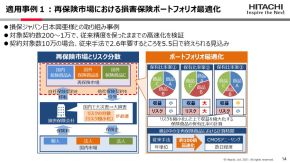

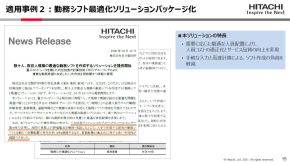

このチクタク開発は、企業における研究開発で最も問われる「有用性の壁(事業化の壁)」の問題も突破する原動力にもなった。例えば、損保ジャパン日本興亜は、再保険市場における損害保険ポートフォリオ最適化にCMOSアニーリングを採用している。2020年10月には、日立としてCMOSアニーリングをベースとする「勤務シフト最適化ソリューション」をリリースし、同ソリューションは三井住友フィナンシャルグループに採用された。

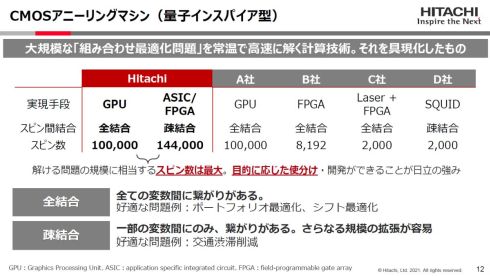

現在、日立が提供するCMOSアニーリングマシンは、GPUを用いるシステムと、同社の独自チップ(ASIC)とFPGA用いるシステムを用意している。解ける問題の規模に相当するスピン数は最大で、目的に応じた使い分け、開発ができることが強みだ。

ムーンショット型研究開発事業でゲート型量子コンピュータの開発へ

CMOSアニーリングマシンで事業化を含めて一定の成果を得た日立が次に取り組みを始めた量子コンピューティング技術が、より汎用性が高いものの実用化のハードルも高いとされるゲート型量子コンピュータである。

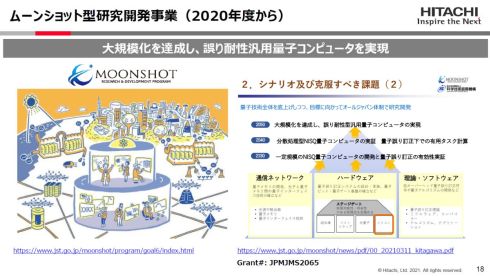

JST(科学技術振興機構)が2020年度から推進している「ムーンショット型研究開発事業」の研究開発テーマの一つとして、大阪大学 教授の北川勝浩氏がプログラムディレクターを務める「2050年までに、経済・産業・安全保障を飛躍的に発展させる誤り耐性型汎用量子コンピュータを実現」があり、日立は4つあるゲート型量子コンピュータのうちシリコン半導体技術をベースとする技術の開発に加わっている。

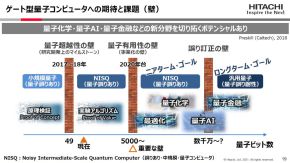

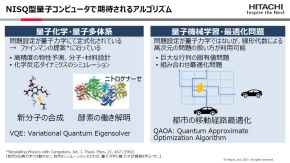

水野氏は「かつては夢の存在だったゲート型量子コンピュータだが、近年研究開発が急ピッチで進み、古典コンピュータを超える『量子超越性の壁』はクリアできている。現在はNISQ(Noisy Intermediate-Scale Quantum:ノイズあり中規模量子デバイス)のシステムが開発できており、次に突破すべき壁は『量子有用性の壁』になる。2020年代にクリアできる可能性があり、そこで量子化学や量子多体系、量子機械学習や最適化問題に適用できるようになるだろう。最終的には『誤り訂正の壁』を超えれば、真の汎用量子コンピュータを開発できるが、ムーンショット型研究開発事業では2050年の達成が目標になっている」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.