Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫く:Arm最新動向報告(6)(2/3 ページ)

2019年10月6〜8日にかけてArmが年次イベント「Arm TechCon 2019」を開催した。本連載では、同イベントの発表内容をピックアップする形で同社の最新動向について報告する。まずは、Armのこれまでの方針を大転換することとなった、ユーザーに独自命令を組み込むことを許す「Custom Instruction」について紹介しよう。

「Custom Instruction」の構成

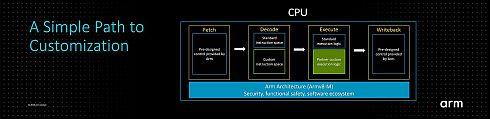

なぜ? と言う話は後で触れるとして、カスタム命令の構成から紹介しよう。基本的には既存の「Cortex-M33」コアのFetch(フェッチ)/Writeback(ライトバック)はそのままで、Decode(デコード)部にカスタム命令用の「枠」が用意され、またExecute(実行)部にカスタム命令用のロジックを顧客が追加できるようになっている(図5)。

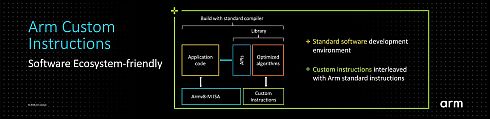

このカスタム命令は、Architecture Licenseの「Armv8-M」から見れば未定義命令ということになるので、そのままだと利用はできない。ここに関しては、そのカスタム命令を作成する顧客がライブラリでそのカスタム命令をサポートする形で、従来の開発環境に統合できるとする(図6)。この「Custom Instructions Extension」を最初に実装するのはCortex-M33、という話は先に述べた通りで、次いで“all future v8-M class”とあるように、今後のCortex-M製品には標準で搭載されるとする(図7)。そして、最後のポイントが、このCustom Instructions Extensionは無償での提供となる(図8)。要するに標準機能扱いになる訳だ。

図7 逆に言えば「Cortex-M0/M0+/M3/M4/M7」に関してはこれは提供されない、という話である(この事実はArmに確認済み)。なお、Cortex-M23に関しては今後提供する予定だそうだ(クリックで拡大) 出典:Arm

さて、これだけだとイメージがわかないと思うが、Arm TechCon 2019の3日目に行われたピーター・グリーンハルシュ(Peter Greenhalgh)氏(Arm VP of Technology and Fellow)の基調講演ではもう少し具体的な話が出てきた。先にも書いたが、デコード段はあらかじめ用意されているカスタム命令用の枠が用意されており、このカスタム命令を呼び出すと、これまでだと未定義命令で例外を発生していたのに対し、Issue(命令発行)段でカスタムロジックを呼び出す制御I/F(インタフェース)が追加されている。その制御I/Fからカスタムロジックを呼び出す、という仕組みである(図9)。

図9 一見目立たないが、スライド右上には“From Cortex-M to Cortex-A”とサラっと書かれており、将来はCortex-Aにもこの拡張命令を提供する予定であることが分かる(というか、そうでないとこの図がいろいろとつじつまが合わなくなる)(クリックで拡大) 出典:Arm

このCustom Instructionの例がこちら(図10)。これは疑似コードだが、例えばBLDCモータをベクトル制御するなんて場合には、短い周期で細かくパラメータを変化させながらI/Oポート経由で出力する、といったことになるから、実はCPUの負荷が非常に高い。MCUメーカーの中には、こうした処理を外付けのアクセラレータでやらせるような仕組みを取っている所もあるが、このアクセラレータをCustom Instructionとして実装できるようになる。

図10 アクセラレータとしてこれらの機能を統合しても良いのだが、命令パイプラインから直接ディスパッチできるのと、I/Oポートなりメモリ経由で呼び出すのと、どちらが高速・低レイテンシかといえば、もちろん命令パイプラインに組み込む方である(クリックで拡大) 出典:Arm

あるいは、最近だと機械学習の推論アルゴリズム(ML Inference)向けの機能をMCUに統合しようなんて話が増えているが、ここで畳み込みの処理をカスタム命令として実装することで、大幅にスループットを引き上げる、なんて実装も可能だ。実際にArmが意図しているのは、こうしたArmv8-Mの命令ベースだと不効率な特定処理を高速化するロジックを、カスタム命令として統合できるようにするという話である。

ちなみに、さらに細かい話をトーマス・エンセルグエイ(Thomas Ensergueix)氏(Arm Senior Director, IoT/Embedded Business)に話を聞いて分かったのは、以下のようなことだった。

- Custom Instructionとして用意されているのは16命令分で、これまでThumb-2で予約されていたOpCodeが割り当てられる

- Operandは最大3つまで。Photo10に出てきたサンプルのように、レジスタ及び(恐らく)即値の指定は可能だが、アドレス指定はできない。多分これはアドレス指定を可能にすると、カスタムロジックからロード(Load)/ストア(Store)ユニットにアクセスを行う必要があり、ところがそうしたI/Fは提供されないためと思われる。このため、アドレス指定が必要になりそうな処理を行う場合、あらかじめArmv8-Mベースでそのアドレスをアクセスするような処理を先に済ませ、その結果をカスタムロジックに渡す必要がある。同様に、カスタムロジック内でメモリアクセスに書き出すような処理も出来ない「はず」である。「はず」というのは、例えばアクセラレータが特定のメモリ領域にDMA(ダイレクトメモリアクセス)を掛けるような処理を、カスタムロジックで可能とするかどうかまで確認していないためだ

- カスタムロジックは通常の実行パイプラインとは分離された形で実装される。このため、カスタムロジックから通常の実行パイプラインを細工するような命令は実装できない(例えば、カスタムプリフェッチ命令を実装する、なんていうことは不可能)

- カスタムロジックのスループットとレイテンシそのものに制約はない。と言ってもスループットの上限はCortex-M側のDecode/Issue段で制限されるから、現状は最高でも1命令/サイクルになる。一方レイテンシは特に制約はないので、例えばレイテンシが100サイクルのカスタム命令を作ることそのものは可能。ただ当たり前だが、このカスタムロジックを処理中は、割り込みのハンドリングなどが全部後回しになるわけで、レイテンシが100サイクルもあると性能に重大なインパクトがあるだろう、という話だった

Copyright © ITmedia, Inc. All Rights Reserved.