“プロセッサ”を開発する東芝メモリ、その技術と狙い:組み込み開発 インタビュー(2/3 ページ)

東芝メモリがプロセッサの開発を発表した。現業から離れているように見えるプロセッサの開発を通じて東芝メモリは何を目指すのか。今回発表された技術の概要と開発の狙いを聞いた。

ビットパラレル方式積和演算器とは

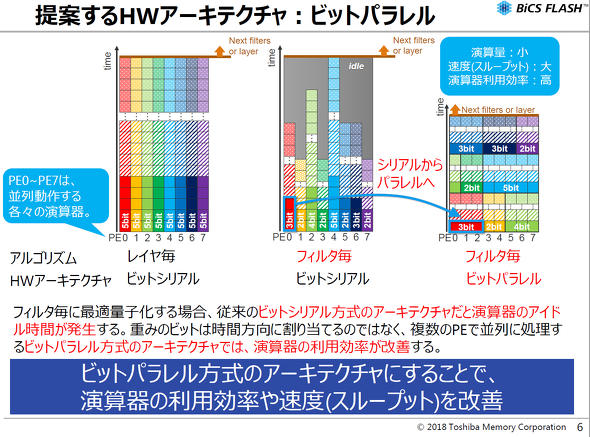

また、同社研究チームは提案アルゴリズムのメリットを最大限に生かすために、新たなアーキテクチャであるビットパラレル方式積和演算器も同時に提案している。

従来のビットシリアル方式では、それぞれのPE(プロセッシングエレメント)が自身に割り当てられたフィルターの積和演算を実行する。この方式では、フィルターごとに演算精度が異なる同社の最適量子化アルゴリズムで問題が発生する。演算量が大きいフィルターを受け持つPEがボトルネックとなり、多くのPEでアイドル状態が発生、プロセッサ全体のスループットが低下してしまう。

今回提案されたビットパラレル方式では、1つのPEが1ビットの積和演算を受け持つ。複数ビットの積和演算は、複数PEの1ビット積和演算結果をそれぞれビットシフトしそれらを加算することで得る。これにより各層内でフィルターごとに演算精度が異なる同社の最適量子化アルゴリズムであっても、演算スループットを最大化しつつ積和演算器の利用効率もほぼ100%まで高めることができる。

2つの新技術で演算サイクルが大幅に削減

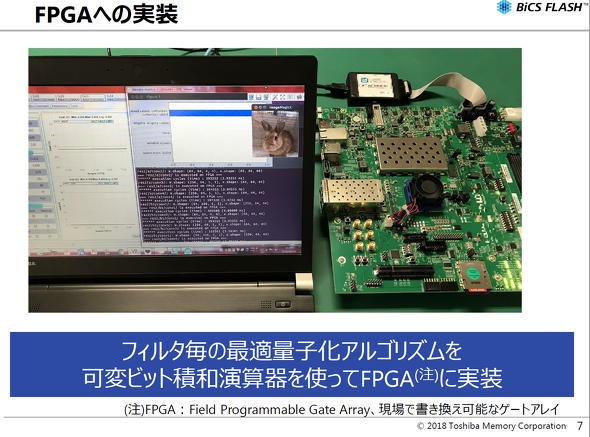

同社研究チームはこれらアーキテクチャをFPGAに実装し、1024個の1ビット積和演算器を並列に持つCNN推論プロセッサを開発した。

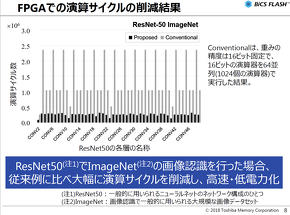

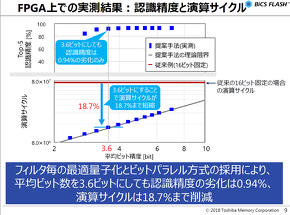

効果検証のためImageNetで学習させたResNet-50の最適量子化ネットワークを作成し、このネットワークで1枚の画像を認識するまでに1024個の演算器が何サイクルの演算を行ったかを示す「演算サイクル」を速度指標として計測した。従来手法との比較のため、16ビット積和演算器を64並列したプロセッサとウェイトが16ビット固定精度の同ネットワークを用いて同様の計測を行った。

効果検証の結果、16ビット固定精度従来手法と比較して大幅に演算サイクルが削減できることが分かった。推論精度がほぼ劣化しない平均演算精度の3.6ビットに量子化した場合、16ビット固定精度モデルから81.3%の演算量を削減できる。これにより、演算スループットは従来手法比で約5.3倍の改善、消費エネルギーも同じく約18.7%まで低減可能だと結論づけている。

推論精度をほぼ低下させることなく大幅に演算量を削減できた要因として、「この技術では量子化の演算精度を固定せず、モデルに応じて細かな粒度で柔軟に調整できる」(藤本氏)ことを挙げる。今回の検証で実行したモデルは量子化が比較的難しいものだったとして、「アプリケーションにもよるが平均1ビットの量子化も狙える」(宮下氏)とする。

なお、今回の発表ではアクティベーション(入力)の演算精度を8ビットと固定しており、「アクティベーションのさらなる量子化も余地がある」(宮下氏)とする。一方で、剪定などの演算量削減手法については採用を避けた。その理由として「剪定などの手法は演算並列性を損なってしまい、むしろ処理が遅くなると考えている。われわれはもともとCNNが有している構造規則性を保ちつつ、計算量を削減する量子化を選択した」と説明した。

Copyright © ITmedia, Inc. All Rights Reserved.