HDLを知らなくてもFPGAの力を引き出せる、インテルが無償のOpenCL開発環境:組み込み開発ニュース(2/2 ページ)

日本アルテラは、FPGAでOpenCLを扱うためのソフトウェア開発環境「Intel FPGA SDK for OpenCL」の最新バージョン「17.1」について説明。従来のコマンドラインベースのツールから、GUIを用いた統合開発環境となるとともに、新たに高速のエミュレータとコンパイラが加わった。

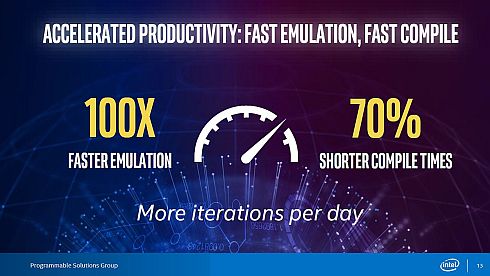

エミュレータは100倍高速化、コンパイラは処理時間を70%短縮

新機能も加わった。従来比で処理速度を100倍高速化したというOpenCLエミュレータと、処理時間を70%短縮できるOpenCLコンパイラだ。フリーベ氏は「これらにより、ソフトウェア開発サイクルをより早く回せるようになる」と強調する。

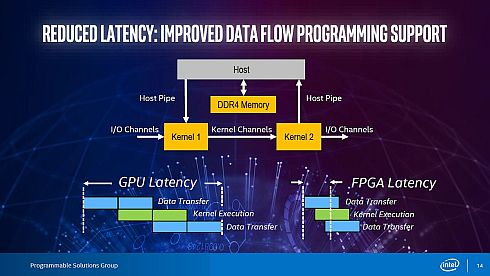

また、並列コンピューティングにおける遅延(レイテンシ)が短いというFPGAの特徴をOpenCLでも活用できるようになったことも大きな特徴だ。並列コンピューティングで広く用いられているGPUの場合、CPU上のホストソフトウェアを介したメモリアクセスが必要ため一定の遅延が発生する。FPGAで並列コンピューティングを行う場合、CPU上のホストソフトウェアを介する必要が無いためGPUよりも遅延が少なくて済む。最新バージョンの17.1では、OpenCLでもこの特徴を利用できるようになった。

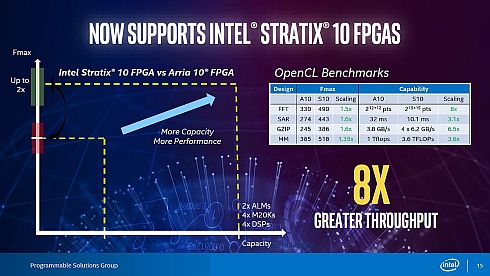

さらに、最新のハイエンドFPGA「Stratix 10」にも対応した。Stratix 10を用いたOpenCLのベンチマークでは、ミッドレンジの「Arria 10」と比べて最大8倍もの処理能力が得られるという。

なお、OpenCLを用いたFPGAプログラミングでは、HDLを用いて最適化する場合と比べて一定の性能ロスがある。フリーベ氏は「OpenCLと比べれば、HDLを扱える専門の技術者が開発した方が最終的には性能は上回るだろう。しかし、一般的なソフトウェア開発者が早いサイクルでFPGAを用いた開発を行い、Time to Marketを実現できることに大きな価値がある」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

いまさら聞けない FPGA入門

いまさら聞けない FPGA入門

あなたは、人に「FPGA」を正しく説明できるだろうか? いまや常識となりつつあるFPGAについて、あらためてその概念から仕組み、最新動向までを解説する。(編集部) 限界に達したエンベデッド・プロセッサを並列処理で補完する

限界に達したエンベデッド・プロセッサを並列処理で補完する

組み込みシステムの能力を並列処理で補完するアイデアは、身近で現実味を帯びたものとなっています。しかし、その実行に際しては手法の選択が重要な意味を持ちます。OpneMPやOpenCLなどを理解しながら、最適な手法を検討しましょう。 「Xeon」とFPGAをシームレスに連携、「インテルPAC」でソフト開発が容易に

「Xeon」とFPGAをシームレスに連携、「インテルPAC」でソフト開発が容易に

インテルがFPGAユーザー向けのイベント「インテルFPGAテクノロジー・デイ」を開催。サーバ向けプロセッサ「Xeon」とFPGAがシームレスに動作する「インテル プログラマブル・アクセラレーション・カード(PAC)」を国内向けに初披露した。 ミッドレンジFPGAでディープラーニング、NVIDIA「Tesla M4」以上の効率を実現

ミッドレンジFPGAでディープラーニング、NVIDIA「Tesla M4」以上の効率を実現

インテルは、AI(人工知能)に関するプライベートイベント「インテル AI Day」の展示会場において旧AlteraのFPGA製品を用いたAIのデモを行った。ミッドレンジFPGA「Arria 10」を用いたディープラーニングの消費電力当たりの処理速度は、NVIDIAのGPUアクセラレータ「Tesla M4」を用いる場合を上回るという。 インテルアーキテクチャもディープラーニングに有効、「GPUが最適は先入観」

インテルアーキテクチャもディープラーニングに有効、「GPUが最適は先入観」

インテルが人工知能(AI)技術や事業、ビジョンについて説明。買収企業の技術を取り入れたAIプラットフォーム「Nervana」により、小から大まで規模に応じてスケーリングさせられるAI技術を提供する。GPUが最適というイメージが強いディープラーニングについても「それは先入観にすぎずインテルアーキテクチャのようなCPUも十分に有効」とした。 FPGAを活用した並列コンピューティングが加速、アルテラがOpenCL向けSDKを発表

FPGAを活用した並列コンピューティングが加速、アルテラがOpenCL向けSDKを発表

FPGAを並列コンピューティングの計算資源として活用するための取り組みを進めてきたアルテラは、FPGA業界初をうたう「OpenCL向けソフトウェア開発キット(SDK)」を発表した。このSDKにより、回路設計の知識のないソフトウェア開発者でもFPGAベースのアプリケーションを、迅速かつ容易に開発できるようになるという。