連載

周辺機器の充実した「MAX 10 NEEK」で本格的な開発を目指す:MAX 10 FPGAで学ぶFPGA開発入門(8)(6/6 ページ)

FPGA開発において周辺機器(回路)は見落とせない要素の1つ。タッチパネルや各種出入力などを備えた「MAX 10 NEEK」を導入して、本格的な開発を目指す。

List 2: //======================================================= // This code is generated by Terasic System Builder //======================================================= module NEEK_LED( //////////// CLOCK ////////// input ADC_CLK_10, input MAX10_CLK1_50, input MAX10_CLK2_50, input MAX10_CLK3_50, //////////// LEDR ////////// output [9:0] LEDR, //////////// HEX ////////// output [6:0] HEX0, output [6:0] HEX1, //////////// PS2 ////////// inout PS2_CLK, inout PS2_CLK2, inout PS2_DAT, inout PS2_DAT2 ); //======================================================= // REG/WIRE declarations //======================================================= reg[22:0] div_cntr; reg[3:0] dec_cntr; reg[9:0] disp_cntr; //======================================================= // Structural coding //======================================================= initial begin div_cntr = 0; dec_cntr = 0; disp_cntr = 0; end always@(posedge MAX10_CLK1_50) begin div_cntr <= div_cntr + 1; if (div_cntr == 5000000) begin dec_cntr <= dec_cntr + 1; disp_cntr<= 1<<dec_cntr; if (dec_cntr == 10) begin dec_cntr <= 0; disp_cntr <= 0; end end end assign LEDR = disp_cntr; endmodule

List2

おおむね昔のLチカに近いが、一応意図を説明しておけば、外部からは50MHzでクロックが入ってくるので、これを50万回(つまり5M回)ごとにカウントし、内部のdec_cntrというレジスタをインクリメントするとともに、どのLEDを表示するかを定めるdisp_cntrというレジスタを書き換えるというものだ。

LEDは全部で10個なので、dec_cntrが10になったら0に戻している。disp_cntrの方は、右から左にLEDが流れるようにシフト演算の形で1の値の位置を移動している。これをassignでLEDR(LED出力)に割り当てて完了である。

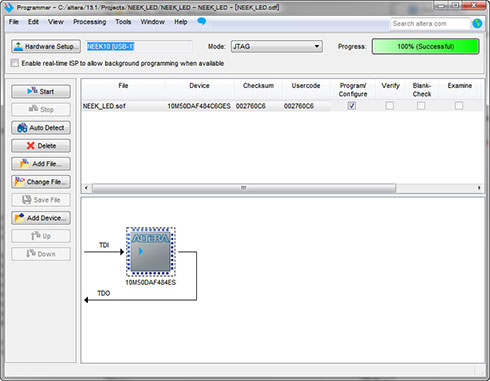

これをコンパイルすると特に問題なく生成されるはず(筆者のマシンだと46秒ほど要した)なので、Programmerを使って書き込んでやると完了である(Photo20)。プログラミングが終わると、こんな具合にLEDが流れるように点滅するはずだ(Movie02)。

Photo20:搭載されるMAX 10は10M50DAF484ESで、MAX 10 Evaluation Kitに搭載されていた10M08SAR144ESと比較するとLE数は8K→50Kに、Flash Memoryは144KB→484KBに、それぞれ強化されている。メモリも378Kbit→1638Kbitと4倍になっており、NIOS IIを使うにも支障はなさそう

Movie02:MAX 10 NEEKによるLチカ

ということで今回はMAX 10 NEEKを紹介した。来月はここにNIOS IIも組み込んで、もう少し本格的に取り組んでみたい。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGAのソフトコアCPUをベンチマークで測定する

FPGAのソフトコアCPUをベンチマークで測定する

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。 FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。