FPGAのソフトコアCPUをベンチマークで測定する:MAX 10 FPGAで学ぶFPGA開発入門(7)(2/6 ページ)

FPGA「MAX10」に「NIOS II」と呼ばれるソフトIPコアを導入することで、ソフトコアCPUを構築できる。ではその処理能力はどれほどか。ベンチマークソフトで測定してみよう。

NIOS IIの処理能力をベンチマークで測定する

ということで無難にNIOS IIが利用可能になったところで、もう少し遊んでみることにする。取りあえず知りたいのは「NIOS IIがどの程度の処理性能を持つか」である。こういう場合、何かしらのベンチマークを走らせてみるのが一番手っ取り早い。ということで、Dhrystoneを走らせてみた。

Dhrystoneそのものはいまさら説明は要らないと思うが、非常に古くから使われている整数演算用ベンチマークである。幸いな事に、現在でもベンチマークは探せば入手できる(ここなど)ので、まずは入手して適当に展開しよう。必要なファイルはdhry.h(ヘッダファイル)、dhry_1.c(メインルーティン)、dhry_2.c(サブルーティン)の3つである。

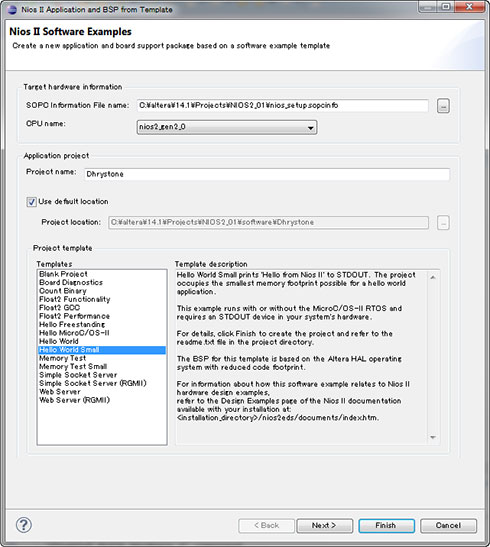

さて、まずハードウェア(つまりQuartus IIで直接記述する方)はそのままにして、まずはソフトウェアだけ入れ替えてみる。まずはここと同じ手順で、別の名前で新しいプロジェクトを立ち上げる(Photo02)。

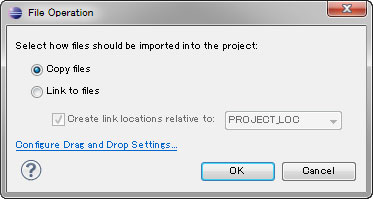

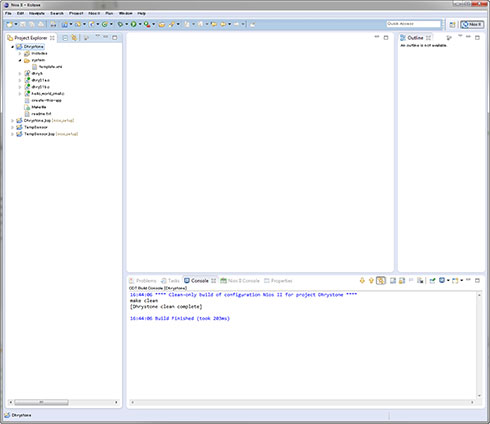

次に、Project Explolerのウィンドウに、先ほどダウンロードしたdhry.hとdrhy_2.cをドラッグアンドドロップで投入する。すると「コピーかリンクか」を聞いてくる(Photo03)ので、どちらか好きなほうを選択(筆者はコピーを選んだ)すると、Project Explolerにこれが追加される(Photo04)。ちなみにdhry_1.cであるが、こちらは中身をコピーして、自動生成されるhello_world_small.cにそのまま貼り付けた。

さて、これをコンパイル……してもさすがにそのままでは通らない。そこで、最低限の変更をする。変更はdhry_1.c(の中身をコピーしたhello_world_small.c)だけである。List 1がオリジナルのdhry_1.cであるが

- 経過時間の計算やDhrystoneスコア計算のためにfloat型を使っている

- 何回ループを回すかをSTDINから入力する

- 出力結果をファイルに出力する

といったコードが入っており、このあたりはテストをするのに不要なのでまるまる削除した。ちなみにループ回数は

/*

printf ("Please give the number of runs through the benchmark: ");

{

int n;

scanf ("%d", &n);

Number_Of_Runs = n;

}

printf ("\n");

printf ("Execution starts, %d runs through Dhrystone\n",Number_Of_Runs);

*/

Number_Of_Runs = 100000;

という具合に10万回の決め打ちにしている。性能を比較するだけだからこれで十分であろうという判断だ。

もう1つの変更は時間測定である。もともとのコードでは、ベンチマーク開始直前と終了直後にclock()という関数で現在のシステム時間をmsec単位で取得してここから性能を測定しているが、NIOS IIの環境ではこれが利用できない。そこで代わりにNIOS IIのHAL APIのTimestamp機能を利用した。

具体的にはまずalt_timestamp_start()を呼んで初期化した後、ベンチマークの前後でalt_timestamp()を呼び出してタイムスタンプ値を取得、後でこれを引き算して経過時間を取得して表示する形にした。ちなみにこのalt_timestamp_start()やalt_timestamp()を利用するためには、冒頭に

#include "sys/alt_timestamp.h" #include "alt_types.h"

を追加する必要があり、またalt_timestamp()の戻り値はalt_u32型なので、これにあわせて変数宣言を変更している。List 2がこれらの変更を行ったソースコードである。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FPGA上でソフトコアCPUを動かす手引き

FPGA上でソフトコアCPUを動かす手引き

これまでFPGAの開発基礎としてLチカなどを紹介してきたが、今回はちょっと目先を変えてFPGA上でのCPUコア動作に取り組む。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

よろしいならばダイナミック点灯だ――FPGAでLEDをダイナミックにLチカさせる

単純なLチカならばFPGAでもそう難しくない。ただ、ダイナミック点灯やそれに伴うソースの最適化については“ならでは”のポイントが散見される。今回も連載で利用している「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAのLED制御プログラムを深く理解する

FPGAのLED制御プログラムを深く理解する

FPGA開発に必要なHDLへの理解を深めるため、MAX 10に用意されているArduino I/Oを利用してのLチカを行い、多灯LEDの制御を含めたプログラミングも解説する。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 FPGAでのLチカをVerilog HDLで理解する

FPGAでのLチカをVerilog HDLで理解する

今回はFPGAでのLチカを例に、FPGA開発に必要なハードウェア記述言語の解説をしたい。用いる「Verilog HDL」はArduinoやCの経験がある方なら、理解そのものはそう難しくないと思う。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 「MAX 10 FPGA」のテスト環境を構築する

「MAX 10 FPGA」のテスト環境を構築する

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。 なぜFPGAが注目されるのか、開発ボードに触れて確認する

なぜFPGAが注目されるのか、開発ボードに触れて確認する

最近では「FPGAの重要性」について語られる機会が増え、適用事例も増加している。ではなぜ今FPGAなのか。実際の開発ボードでFPGAを学びながら、FPGAへの理解を深めよう。連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントもご用意。