ニュース

SoCのテスト時間を3分の1にするテストソリューション、ケイデンス「Modus」

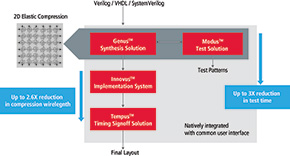

ケイデンスがSoC設計のテスト時間を最短で3分の1に短縮可能なDFTツール「Modus Test Solution」を発表した。

Cadense Design Systemsは2016年2月2日(米国時間)、SoC(System on Chip)設計のテスト時間を「最短で3分の1に短縮可能」(同社)なテストツール「Modus Test Solution」を発表した。

新ツールは「2D Elastic Compression」と呼ぶアーキテクチャの導入により、デザインサイズや配線に影響を与えずに400倍を超える圧縮率を実現しており、加えて、ATPG(automatic test pattern generation)の実行中に複数スキャンサイクルをまたいだケアビット制御が可能であることから、高圧縮であっても高い故障検出率を維持している。

またIPコア内蔵メモリのセルフテスト(PMBIST)実行時にシェアードテストアクセスバスを挿入可能であり、FinFET SRAMや自動車の安全性アプリケーションなどのテストアルゴリズムも挿入できる。DFTロジックやGenusなどで共有される新しく統合されたTCLスクリプト記述およびデバッグ環境を用いるATPG機能も用意されている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングに向けた、ハードウェアアクセラレーションの選択肢

組み込みコンピューティングを加速させるハードウェア・アーキテクチャとは何でしょうか。DSP?GPU?それともメニーコアでしょうか。どのアプローチが最も適するのかを考察します。 FinFET革命がコンピュータアーキテクチャを変える

FinFET革命がコンピュータアーキテクチャを変える

FinFETの登場により、ムーアの法則はまだ継続される見通しです。ですが、それで全てが解決するわけではありません。FinFETの登場が、大きなSoCを自律的な機能ブロックに分割するという方向に導く結果となるでしょう。 ISO26262準拠に必要な故障注入検証の手間を半減、ケイデンスが新ソリューション

ISO26262準拠に必要な故障注入検証の手間を半減、ケイデンスが新ソリューション

Cadence Design Systems(以下、ケイデンス)は、自動車向け機能安全規格であるISO 26262に準拠するICを設計する上で必要な故障注入(Fault Injection)と安全性検証を行うプロセスに掛かる手間を半減する「Incisive機能安全ソリューション」を発表した。 ザイリンクスとケイデンス、Zynq向け仮想プラットフォームを開発

ザイリンクスとケイデンス、Zynq向け仮想プラットフォームを開発

ザイリンクスとケイデンス・デザイン・システムズは、拡張性を備えたZynq-7000 EPP向けバーチャルプラットフォームを共同開発し、ソフトウェア主導のアプローチを組み込みソフトウェア開発者に提供する。