“印刷”のCortex-M0から64bit化を推進するCortex-A35、mbed OSまで、ARMの示す未来像:ARM TechCon 2015基調講演リポート(2/4 ページ)

英ARMが同社の取り組みを紹介する「ARM TechCon 2015」を開催した。内容は多岐にわたるが、ここではCTO Mike Muller氏による基調講演から、ローエンド64bitCPUやセキュリティ、mbed OSなど、ARMの目指す未来像について紹介する。

広まるARMサーバの輪

さて、ここまでの話はいわば前振りで、ここからが本題。ARMは“Sensors to smartphones to servers”ということで、ローエンドデバイスからハイエンドサーバまで幅広い範囲を狙う製品群を提供しようとしてるわけだが(Photo08)、こちらに関して「ARMからの」新製品はない。

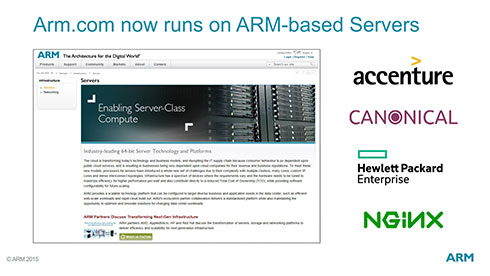

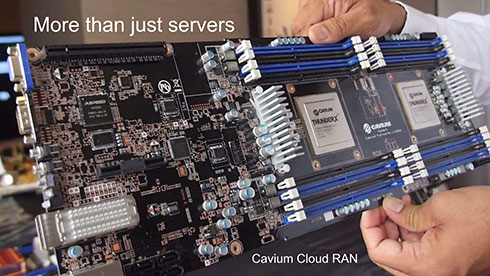

ただ多くのパートナーが既にARMベースのサーバ向けSoCを製造・発表しており、今回はそれらを利用したサーバ製品が既に多く存在する事がアピールされ(Photo09)、既にARMのサイトがARMベースに置き換わった(Photo10)事や、Caviumが2015年7月に発表したThunderXプロセッサベースのブレード(Photo11)、さらには幾つかのHPCシステムがARMベースで構築を始めた事などが紹介されるなど、サーバ向けに普及が始まりつつあることが示された。

Photo09 Applied Microはスポンサーセッションのパネルディスカッションの折に、X-Gene 3のアナウンスを行い「TSMCの16FF+を利用して3GHz動作を目指す」としている。2016年中にサンプル出荷を予定しているそうだが、ただプレスリリースが出ていないあたり、まだ完全に正式なアナウンスではないのかもしれない

64bit化を推進する「Cortex-A35」

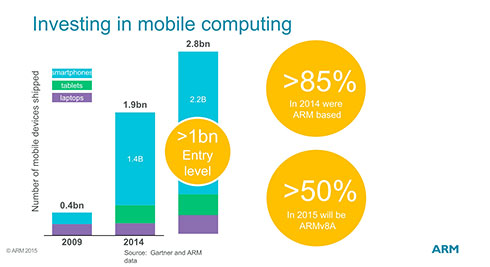

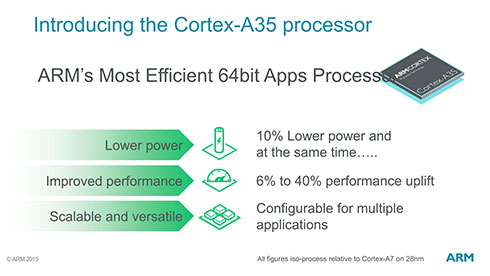

次が新製品であるCortex-A35の紹介である。2014年には全部で19億台のMobile Deviceが存在しており、これが2020年には28億台に増えると予測されているが、この28億台のうち、エントリーレベルにあたるスマートフォンやタブレットはおよそ10億台を超えるとARMは予測している。

しかもOSやアプリケーションが64bitに順調に対応が進んでいる事もあり、既に現時点で5割以上が64bit対応になっており、2020年にはこの比率がさらに高まるとみられている。この急速な普及により、“Mobile-first”という形に社会が変わってゆくとする(Photo14)が、このためにはより低価格で実現できるコアが必要とARMは判断した。

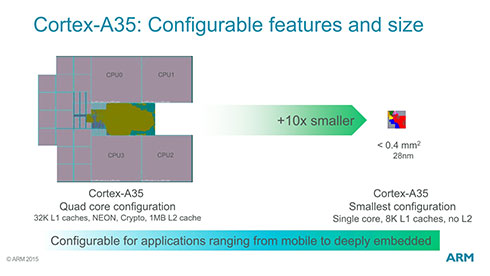

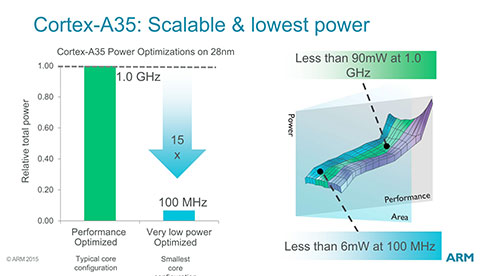

具体的なターゲットはCortex-A5/A7の後継の64bitコアである(Photo15)。つまり、性能的には既存Cortex-A53の下に位置するものとなる。興味深いのはそのスケーラビリティで、100MHz動作ではわずか6mWで動作する事だ。ちなみに1GHzでは90mWとなっており、これもアプリケーションプロセッサとしてはかなり低い部類に入る。またダイエリアもシングルコア/L2キャッシュなしだと0.4平方mmまで縮小できる。

Photo15 Cortex-A35は一部の命令だけデュアルイシューとなる(つまり大半の命令はシングル)インオーダー型のパイプラインで、これもほぼCortex-A7に近い。ただ別にCortex-A7を64bit化した訳ではないとの事

実際、Cortex-A35のターゲットはローエンドのスマートフォンだけではなく、ウェアラブルデバイスなども視野に入れているとの事。ライフログ系のみならずスマートウォッチに関しても第一世代ではCortex-MベースMCUのケースが非常に多く、64bitのアプリケーションプロセッサが入る余地はないのだが、今後より高機能化が進む、あるいはセンサーハブ的な機能が入るようになると、どうしても処理性能が必要になってくるわけで、こうしたものまでがCortex-A35のターゲットになる。

Photo16 ここでは1GHzをターゲットにしているが、実際はCortex-A53と同じ程度まで動作周波数を上げられるとの事。棒グラフの下側が切れているが、青は"Smallest core configuration"である

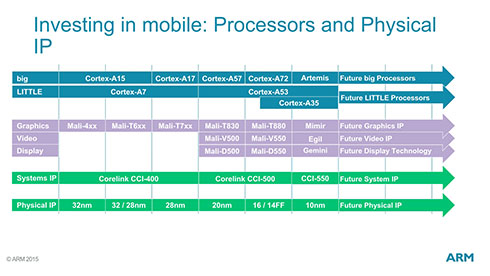

最後に今後のロードマップが示された(Photo18)が、直近で言えばハイエンドがもう一度刷新されるほか、GPU/Video/Displayに新製品が予定されている模様だ。これらは10nmがターゲットなので2015年中ということはありえず、早くても2016年後半になりそうだが。

Copyright © ITmedia, Inc. All Rights Reserved.