連載

「MAX 10 FPGA」のテスト環境を構築する:MAX 10 FPGAで学ぶFPGA開発入門(2)(5/7 ページ)

今回から実際に「MAX 10 FPGA評価キット」を利用しての開発に着手する。まずは環境構築だ。キット以外に必要なモノもあるので注意して欲しい。今回も連載で使う「MAX 10 FPGA 評価キット」の読者プレゼントをご用意。

ちなみに、これで生成されたソースコードは以下「List1」になる。

ソースコードの説明はまた次回以降に説明するとして、これをこのままコンパイルしてファイルを生成、ダウンロードしてもLEDに変化はない。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Axelsys

// Engineer: Greg Miller

//

// Create Date: 11:21:08 08/21/2014

// Design Name: LED

// Module Name: LED_Verilog

// Project Name: Altera MAX10 Breakout Board

// Target Devices: 10M08SAE144C7G

// Tool versions: 14.0

// Description:

// LEDs, D1 through D5 will blink on for 1/2 second and off for 1/2 second.

// Clock is operating at 50MHz.

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LED_Flash_all(

input clk,

output LED1,

output LED2,

output LED3,

output LED4,

output LED5

);

reg[15:0] div_cntr1;

reg[9:0] div_cntr2;

reg dec_cntr;

reg half_sec_pulse;

initial begin

div_cntr1 = 0;

div_cntr2 = 0;

dec_cntr = 0;

end

always@(posedge clk)

begin

div_cntr1 <= div_cntr1 + 1;

if (div_cntr1 == 0)

if (div_cntr2 == 762)

begin

div_cntr2 <= 0;

half_sec_pulse <= 1;

end

else

div_cntr2 <= div_cntr2 + 1;

else

half_sec_pulse <= 0;

if (half_sec_pulse == 1)

dec_cntr <= !dec_cntr;

end

assign LED1 = dec_cntr ;

assign LED2 = dec_cntr ;

assign LED3 = dec_cntr ;

assign LED4 = dec_cntr;

assign LED5 = dec_cntr ;

endmodule

*****

そこで最後の5行を書き換えてみた。

assign LED1 = dec_cntr ; assign LED2 = dec_cntr ; assign LED3 = dec_cntr ; assign LED4 = dec_cntr; assign LED5 = dec_cntr ;

から

assign LED1 = dec_cntr ; assign LED2 = !dec_cntr ; assign LED3 = dec_cntr ; assign LED4 = !dec_cntr; assign LED5 = dec_cntr ;

に変更してみた。

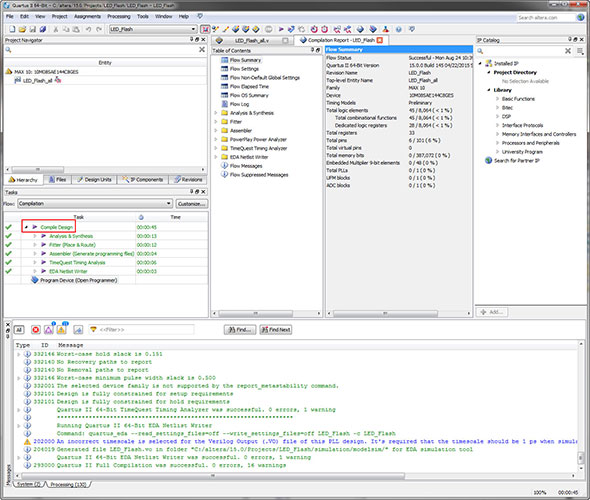

dec_cntrは0か1の値を取り、0ならLEDが消灯、1なら点灯する。そこでLED 1/3/5とLED 2/4に与える値を反転させることで、互い違いに点滅させようというものだ。この変更をQuartus IIの画面上で行ったら、やはり左側、Entityの下にある“Tasks”画面で“Compile Design”をクリックすると、問題がなければ数分(環境による:2回目以降は1分かからなかった)後にコンパイルが完了するはずだ(Photo25)。

Copyright © ITmedia, Inc. All Rights Reserved.