第39回 IBISのPackage Model:前田真一の最新実装技術あれこれ塾(2/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第39回はIBISのPackage Modelについて解説する。

2.PackageのR、L、C定義

ここでIBISのPackage定義を見ると、1段のR、L、Cの回路になっています。しかし、長さ情報がないので、これは伝送線路に回路ではなく、遅延のない、単純なアナログ回路となっています。配線を伝送線路として考慮しなければならないのか、遅延のない理想線路として考えて良いのかは、信号の立ち上がり、立ち下がり速度と、配線の長さの関係で決まります。

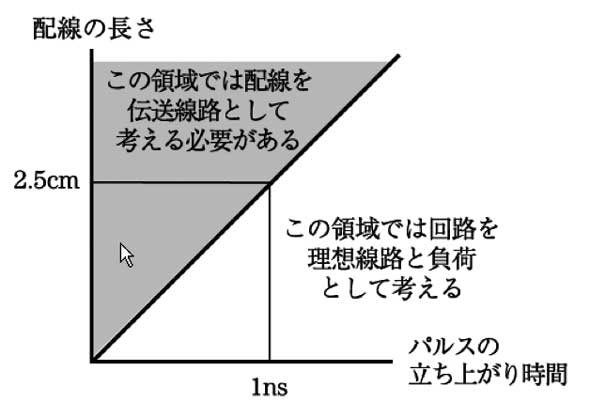

一般的には信号の立ち上がり/立ち下がり時間が1ns程度、配線長が2.5cm程度以下であれば、伝送線路として考えなくてもよいといわれています(図7)。

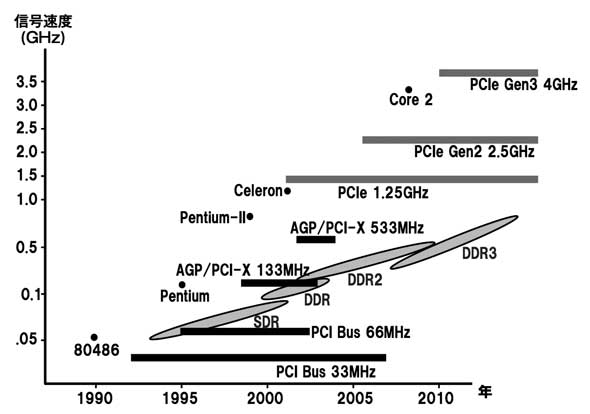

IBIS規格を初めて制定したときは、PCI並列バスをターゲットに開発されていました。そのときのPCIバスクロックは33MHzで将来構想としても66MHzが想定されていました。その、33MHz、66MHzの信号の立ち上がり、立ち下がり時間は1ns程度が想定されていました。その当時はパッケージ内配線の長さはせいぜい1cm程度で、パッケージ内は伝送線路として考えない領域でした。このためIBISモデルのパッケージモデルは、R、L、Cの集中定数モデルとして考えるのが適当でした。しかし、この20年で信号速度は100倍に高速化しました(図8)。

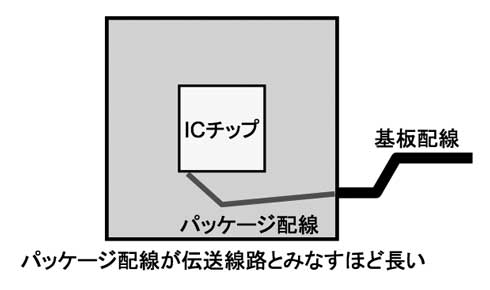

逆に、ICの集積度の向上により、ICのピン数が増大し、パッケージ内基板(インタポーザ基板)の配線長が増大しました。現在の高速信号では、パッケージ内配線も伝送線路として解析しないと、正しい信号化波形の解析は行えません。多くの伝送線路解析シミュレータでは、ICチップのパッド波形とICパッケージのピン波形の両方をシミュレーションする機能があります。これは、基板内の配線を伝送線路として考える必要がある場合では、基板内の配線によりICチップでの波形と、ICパッケージピンでの波形が異なるからです(図9)。

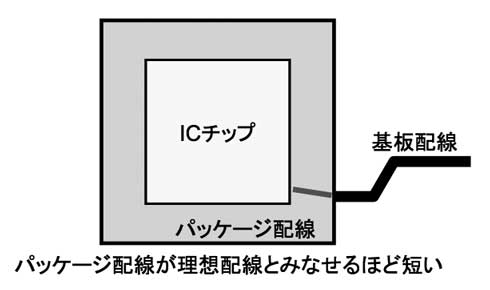

信号の立ち上がり、立ち下がりが遅く、パッケージ内配線が短い場合には、ICチップのパッド波形とICパッケージのピン波形は同じになります(図10)。

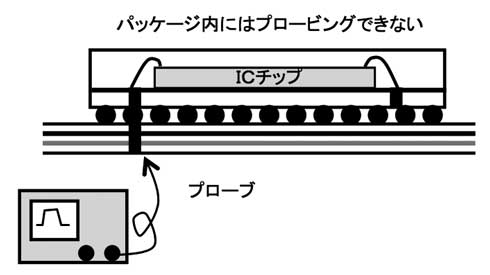

標準のIBIS Packageモデルは、パッケージピントチップパッドの波形には違いは生じないという前提で考えられています。基板上で波形観測をする場合、ICの部品ピン波形は何とか測定できますが、ICパッケージ内部のチップのパッド波形の測定は困難です(図11)。

回路が正常に動作するか、誤動作するかの波形評価は、ICチップのパッド波形の方が精度が高いのは、当然です。ICパッケージピンの測定波形とシミュレーション波形が同じであれば、ICチップのパッド波形はシミュレーション波形で推測ができます。IBISでもその後のバージョンアップで、基板内配線を伝送線路として解析できるようなオプション機能が追加されましたが、残念ながら一部を除いて、このオプション機能を使ったIBISモデルは存在していません。IBISの次のバージョンでは、このPackageモデルが精度の高い伝送線路モデルとして定義される予定です。

Copyright © ITmedia, Inc. All Rights Reserved.