第32回 損失の解析:前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第32回は、前回説明した損失について計算する「損失の解析」について取り上げる。

3.実際の損失

損失には誘電損失と抵抗損失があるため、実際の基板の損失を考える場合、問題が複雑になります。

例えば、表皮効果による抵抗損失は、導体の表面積を小さくすることにより、小さくすることができます(図10)。

しかし、誘導損失は逆に誘電体と接する面が大きくなると電界の影響を受けて回転運動をする電気双極子が多くなり、損失が大きくなります(図11)。

配線幅を太くした方が良いのか、細くした方が良いのかは、誘電体の材料特性や銅箔の表面粗さ、信号の周波数で変わります。

ここでは、参考のため、同じ配線長さで、配線の幅、誘電体の誘電率や誘電損失、誘電体の厚さ、胴体の表面粗さなどいろいろな係数を変化させた場合の損失の変化をシミュレートした結果を紹介します。なお解析はアメリカSinbrian社の「Simbeor」というプリント基板用の3次元フィールドソルバを使用しました。

配線幅の変化

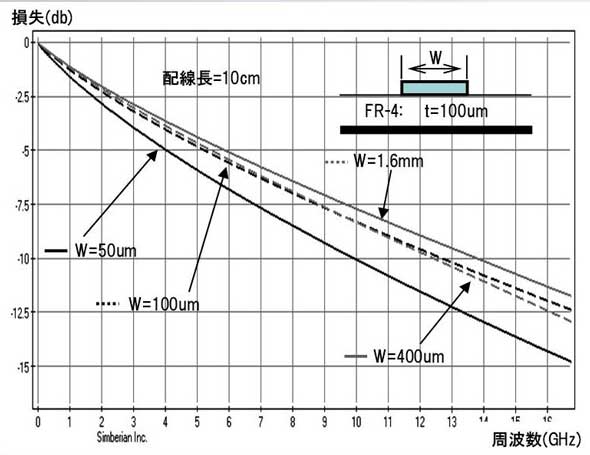

基板表面層を想定して、配線幅を変えた場合の損失を見てみます。

層厚は一定としているので、配線の特性インピーダンスは変化しますが、損失には影響ないように設定しました。

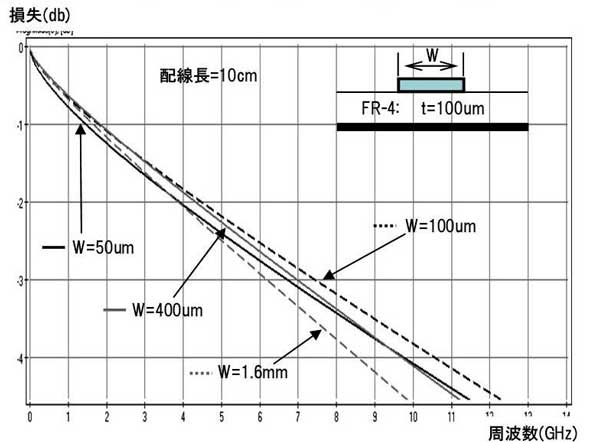

図12はFR-4基板の一般的な誘電率と誘電損失の値を設定してシミュレーションした結果です。

配線幅は50μm、100μm、200μm、400μm、1.6mmで、層厚(配線とプレーンの間隔)は100μmに設定しています。

縦軸が損失(db)で横軸は周波数(GHz)です。損失は0dbが無損失で、マイナスの値が大きいほど、損失が大きくなります。

0Hz(DC)では損失が最も小さく、周波数が上がるにつれて、損失が大きくなります。

図12では線幅と損失の大きさに明確な依存性が見られません。例えば、3GHz以下では最も細い線幅50μmが最も損失が大きいのですが、高い周波数では最も太い線幅1.6mmが損失が大きくなっています。

これは、配線幅と周波数で抵抗損失の影響と誘電損失の影響のどちらが支配的になるかが交錯しているためです。

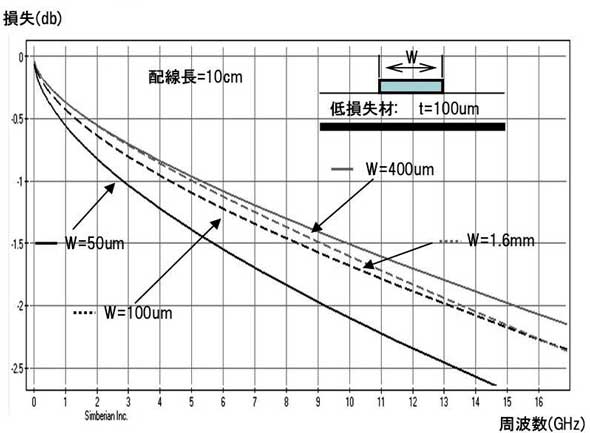

図13は低損失、低誘電率の高周波用基板材料を使った場合のシミュレーション結果です。図13の結果は明確です。

高周波用の材料を使ったことにより、誘電損失が小さくなり、配線幅と抵抗損失の関係が現れています。つまり、線幅が細くなると有効断面積が小さくなり、損失が増大しています。ただし、線幅が太くなると、これでも誘電損失の影響が大きくなり、線幅を太くしても単純な有効断面積の変化よりも損失の低減は小さくなっています。

そして、極端に太い1.6mm幅の配線では、やはり、損失が大きくなっています。

また、誘導損失が減少したため、トータルの損失は減少しています。

図14は、FR-4の材料を使って、銅箔の表面を荒くした場合です。

誘電損失は大きいままですが、逆に抵抗損失を大きくしたので、誘電損失の影響が相対的に小さくなり、配線幅に対して、幅が広くなるほど損失が小さくなっています。今回は配線幅が極端に広い1.6mm幅の損失が最も小さくなっています。

しかし、誘導損失はFR-4と同じで大きく、抵抗損失も大幅に増大しているため、トータルの損失は大きくなっています。

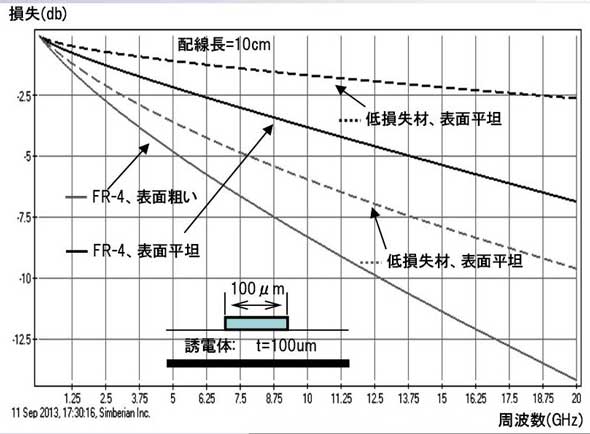

図15は基板でよく使われる100μmの線幅で、導体表面がスムースなFR-4と高周波用低誘電材、導体表面が粗い場合のFR-4と高周波用低誘電材の損失を比較したものです。

当然のことですが、低損失で銅箔表面が平滑な場合の損失が最も小さく、FR-4で銅箔表面が粗い場合が最も損失が大きくなります。

今回の設定では、FR-4で導体表面が平滑な方が、低誘電率で導体表面が粗い場合より損失が小さくなっています。

しかし、実際の基板では、銅箔表面の粗さは基板製造過程での荒れや使用する銅箔などにより変化します。

基板外層配線と内層配線、ビルドアップ方法などでも変化します。

高周波回路用の低損失誘電体は多くの会社が製品を出していますが、まだまだFR-4の方が価格や加工性、銅箔との密着性、熱特性、耐湿性、難燃性など総合的な性能ですぐれています。このため、信号が高速化してきて、損失が気になるようになってきた民生用にはあまり使われていません。

例えば、PCI Expressの規格作成に当たっても、FR-4基板で動作することを条件としています。

この例からも、損失は基板の条件によって、誘電損失と抵抗損失のどちらが影響が大きいかが変化することが分かります。損失を小さくするためには、シミュレーションを利用して、最適設計を行う必要がありますが、そのためには、誘電体や銅箔の正しい情報が必要となります。

残念ながら、この素材の正確な情報は材料のサプライヤ、コアやプリプレグなど基板材料メーカー、銅箔メーカー、これらの材料を加工する基板メーカーのどこがコントロールして値を保障するのかがはっきりしていません。というよりも、誰も最終製品となる基板と正しい値を把握していません。

今後、早急にこのビジネスモデルを確立して、正確な値が伝わるようにする必要があります。

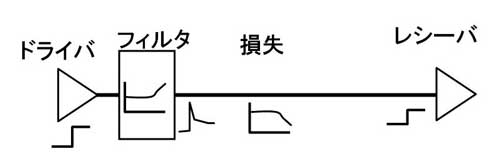

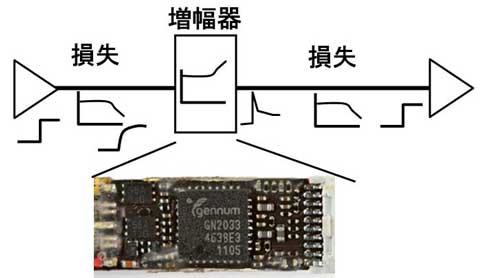

また、損失は周波数依存性があり、周波数の高い信号ほど減衰が大きくなるため、ドライバやレシーバ回路にハイパスフィルタを組み込んで損失の影響を打ち消したり(図16)、配線の途中に信号増幅回路を挿入して信号の減衰を補うなど(図17)、アナログ信号処理の技術をデジタル回路に応用したりしています。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫前田真一の最新実装技術あれこれ塾

摩擦があると、どうしてエネルギーを失うのか

摩擦があると、どうしてエネルギーを失うのか

摩擦によって力学的エネルギーが損失することを理解するためには、まずニュートンの運動方程式をきちんと理解する必要がある。 SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの課題克服へ、新材料を用いたゲート絶縁膜で信頼性を向上

SiC-MOSFETの量産採用に向けた課題の1つとして挙げられているのが、酸化シリコンを用いたゲート絶縁膜に起因する動作時の信頼性の低さだ。大阪大学と京都大学、ローム、東京エレクトロンは、AlON(アルミニウム酸窒化物)を用いたゲート絶縁膜によって、SiC-MOSFETの信頼性を高める技術を開発した。