ARMが「mbed OS」で伝えたいメッセージ:ARM TechCon 2014リポート(前編)(2/3 ページ)

英ARMは2014年10月1〜3日の3日間、同社の取り組みを紹介するカンファレンス「ARM TechCon 2014」を開催した。内容は多岐に渡るが、ここでは「mbed OS」「TSMCとの10nmプロセス協業」などのトピックを紹介したい。

10nmプロセスにおけるTSMCとの協業

ARMはこのカンファレンスの期間中、2014年10月2日(現地時間)に、TSMCと共同で64bit Cortex-Aプロセッサに向けて協業することを発表している(プレスリリース)。

もともとARMはTSMCと長く協業体制を結んでおり、Artisanの物理IPを16nm FinFETプロセス向けに提供している他、28nmではさらにPOP(Processor Optimization Package)やHard IPの提供も行っている。既に28nm世代では28nm HPMプロセスを使って広範に製品を投入しているのは周知の事実であり、そしてTSMCの場合はほとんどの製品が20nmをスキップして16nm FinFETプロセスに移行しつつある。

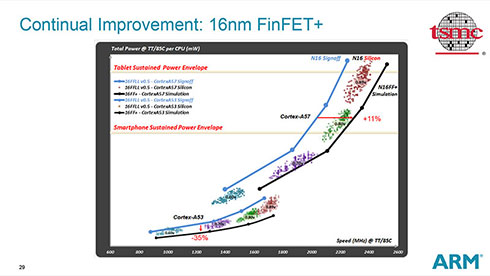

TSMCはこれに加えて16nm FinFET+という若干性能を改善したプロセスを用意しており、こちらの動向についてまとめたのが下の図(Photo07)である。これは同社のCortex-A57コアとCortex-A53コアについて、動作周波数と電圧の関係をまとめたものである。

青線は16nm FinFETプロセスのSign Offにおける想定された動作周波数/電圧の関係、点は実際のシリコンによる特性の実測値、黒線は16nm FinFET+プロセスのシミュレーション値となる。もともとSing Offの際の想定値よりも実際のシリコンの特性は改善している訳だが、16nm FinFET+プロセスではこれがさらに改善されると見ている。省電力方向では従来比で35%削減、動作周波数は最大11%向上するとしており、実際のシリコンに関してはさらに性能が改善する可能性がある。

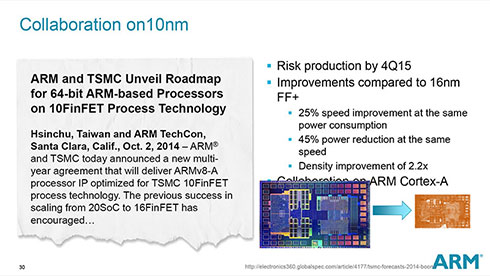

これに続いて示されたのが(Photo08)である。実際のところまだ不明確な部分は多いが、16nm FinFET+プロセスと比較して

- 同じ消費電力なら、動作周波数が最大25%向上

- 同じ動作周波数なら、消費電力が最大45%削減

- ロジック密度が最大2.2倍に向上

といった特性がTSMCの10nm FinFETプロセスの目標であり、2015年第4四半期にリスク生産が開始される見込みとなっている。

ARMは少なくとも、この10nm FinFETプロセスに対応したArtisan物理ライブラリを提供するとしており、長期的にはPOP IPあるいはHard IPの提供の可能性もあるだろう(といっても、まずは16nm FinFET/FinFET+プロセス向けが先行すると思われるが)。

Copyright © ITmedia, Inc. All Rights Reserved.