先進運転支援システムの開発を支える半導体の役割:オートモーティブワールド2014リポート(2/3 ページ)

自動車の次世代技術の専門展示会である「オートモーティブワールド2014」には多数の半導体メーカーが出展した。本稿では、先進運転支援システム関連を中心に半導体メーカーの展示を紹介する。

EVの走行距離を10〜15%伸ばすアクティブセルバランス

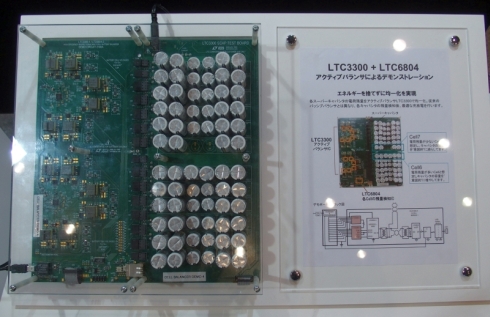

リニアテクノロジーは、電気自動車やプラグインハイブリッド車のリチウムイオン電池パックの実行容量を増やすことができるアクティブセルバランスのデモンストレーションを行った。

同デモでは、同社の第3世代電池監視IC「LTC6804」と(関連記事:リニアが第3世代電池監視ICを発表、「EV/HEV向けでシェア75%が視野に」)、LTC6804と連携してアクティブセルバランスを行えるフライバックコントローラ「LTC3300」を用いている。

リニアテクノロジーのアクティブセルバランスのデモ。ボードの右側にはリチウムイオン電池セルを模擬するためにスーパーキャパシタが直列で接続されている。電池パック内に容量の異なる電池セルがあることを示すため、上から6番目の列は中央の2本の小型スーパーキャパシタがなく、7番目の列は小型の変わりに大型のスーパーキャパシタが入っている(クリックで拡大)

一般的にリチウムイオン電池は、同じ仕様で発注したとしてもその容量にはバラツキがある。数十個の電池セルを用いる電池パックの中には、容量が大きいものと小さいものが混在することになる。アクティブセルバランスを行えば、そういった不均一な容量の電池セルから構成される電池パックでも効率的に充電を行えるのだ。「ユーザーの検討結果によれば、アクティブセルバランスを使えばEVの走行距離を10〜15%伸ばせる。もちろんLTC3300やトランスなどの追加回路が必要になるが、高価なリチウムイオン電池の容量を10%増やすのと比べて、コストや重量増加が少なくて済むというメリットがある」(同社の説明員という。

電力と音楽データを1本のオーディオケーブルで伝送

ロームブースでは、子会社のラピスセミコンダクタが開発中の車載向け直流電源通信ICを展示していた。

この直流電源通信ICを用いれば、電力、データ信号、制御信号を1本のツイストペアケーブルで伝送することができる。データの伝送速度は10Mビット/秒で、電力伝送については2Aまでの電流を流せる。

展示ブースでは、カーオーディオの本体を模したボードに直流電源通信の送信ICを、D級アンプを組み込んだスピーカーを模したボードに同受信ICを組み込んで、一般的な赤白のオーディオケーブルで接続。カーオーディオ本体側ボードで再生している音楽データだけではなく、ボリュームスイッチで制御している音量を変更するための制御信号と、電力を1本のケーブルで伝送していた。ケーブル長は5.6mと長いものの音楽データの伝送などに問題は発生していない。今後の開発課題は、車両内で発生するさまざまなノイズに対する耐性を確保することだという。

車載向け直流電源通信ICのデモ展示。写真左側のカーオーディオの本体を模したボードと、右側のD級アンプを組み込んだスピーカーを模したボードをオーディオケーブルで接続。1本のケーブルで、音楽データと制御信号、電力を伝送している(クリックで拡大)

「ディペンダブルメモリ」とは?

ルネサス エレクトロニクスは、科学技術振興機構(JST)のCREST(Core Research for Evolutional Science and Technology)プログラムの下で共同研究を行っている「ディペンダブルメモリ」を紹介した。

一般的にSRAMは、製造プロセスや経年劣化、周辺環境の変化などによってディペンダビリティと呼ぶ指標が低下する。そして、ディペンダビリティが低下すると動作不良が発生しやすくなる。ディペンダブルメモリは、ディペンダビリティの低下による動作不良を抑制するSRAMの回路技術の総称だ。

今回のディペンダブルメモリの展示は2つある。1つは、2個のメモリセルの間に橋渡し役のトランジスタを追加することにより、冗長性を持った1個の高信頼なメモリセルとして使用できるQoB(Quality of Bit)メモリをシステムレベルで評価するための技術である。

Synopsysのバーチャルプロトタイピングツール「Virtualizer」を使って、キャッシュメモリにQoBメモリを用いたマイコン上で動作するカーシミュレータを用意。電源ノイズなどによってSRAMに不具合が発生した場合に、ミリ秒単位でフェイルセーフ制御を行って事故を回避できることを示した。

QoBメモリを用いたマイコン上で動作するカーシミュレータ。QoBメモリを用いていない場合では、電源ノイズに不具合が発生して車両が列車や側壁に衝突するが、QoBメモリを用いる場合には事故は起こらない(クリックで拡大)

もう1つの展示は、外的要因や経年劣化などによる動作不良を検知/補正する技術である。具体的には、SRAMのメモリブロックの入力電圧が低下するような状態になった場合に、入力電圧を補正したり、読み出しマージンを拡大したりして動作不良を抑制する追加回路となっている。一般的なSRAMの定格電圧は±5%の範囲内でしか動作を保証していないが、この回路を組み込めば±7%まで拡大できる。また、回路の追加によるSRAMアレイの面積増加も0.5%程度で済む。「BIST(Built-in self Test)回路によって定期的にメモリブロックをテストして状態を把握するので、自動車のブレーキパッドのようにマイコンの交換時期を知らせることも可能になる」(ルネサスの説明員)という。

自動車向け機能安全規格であるISO 26262への対応でも、ディペンダブルメモリを活用する余地は大きそうだ。

Copyright © ITmedia, Inc. All Rights Reserved.