第22回 オンチップ電源:前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第22回は、インテルの次世代CPUアーキテクチャ「Haswell」などで注目されてきた「オンチップ電源」について解説する。

第3の理由はLSIの消費電流低減です。今回のHaswellでも、この電源回路をLSI内部に実装して消費電力を改善しようとしています。

現在、CPUをはじめとするLSIでは消費電力を低減するためにきめ細かい電源電圧のコントロールを行っています。

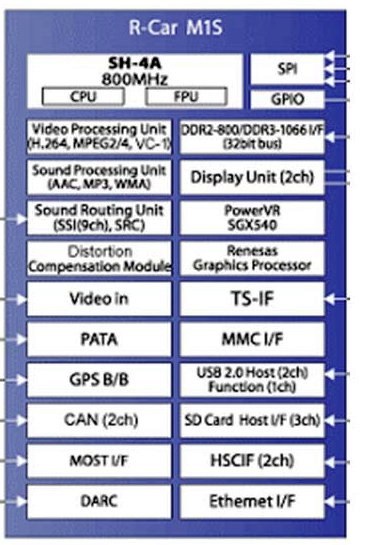

ASICやシステムICは多くの機能ブロックが寄せ集まって一つのLSIとなっています(図10)。これらのブロックは全て動作しているわけではありません。

動作していないブロックの電源電圧を低くしたり、電源をオフしたりすることによりLSIの消費電力を抑えます。

CPUがマルチコア化したのも同じです。CPUの処理に応じて、動作させるコアだけを動かし、動作しないコアの電圧を下げます。Haswellでは、この動作しないコアの電圧をそれまでより低く抑える技術を開発し、ここでも消費電力を抑えています。

Haswellが電源回路をチップに内蔵したのは、この電源電圧コントロールをより素早く、よりきめ細かに行うためです。

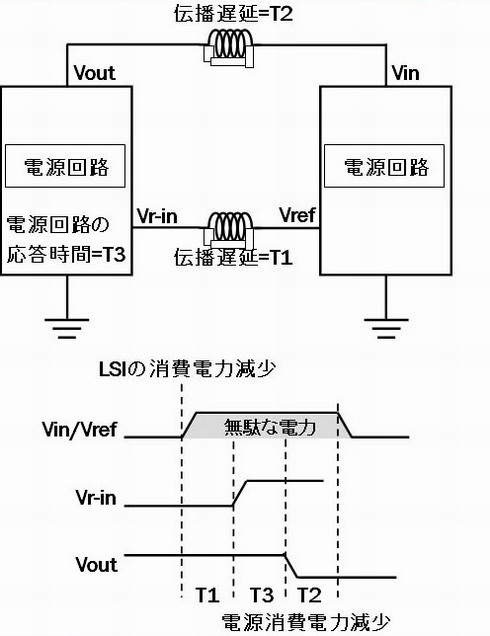

外部の電源は電源電圧モニタをもっていて、LSIから送られてきたチップ電圧情報により、チップの電源電圧が一定になるように出力電圧をコントロールします。このLSIの電圧変動を関知してから、LSIの電圧が正しくなるまでの時間をループ特性と呼びます。

外部電圧の応答時間では、電源装置の応答時間と、PDNの伝播遅延時間が加算されています。

LSIがきめ細かく内部回路の省エネを行っても、実際に電源回路が動作するに移るまでには、遅延が生じます(図11)。

このような無駄は、LSIが細かい動作コントロールを行ってきめ細かく省エネを実行しようとする努力をも無駄にしてしまいます。

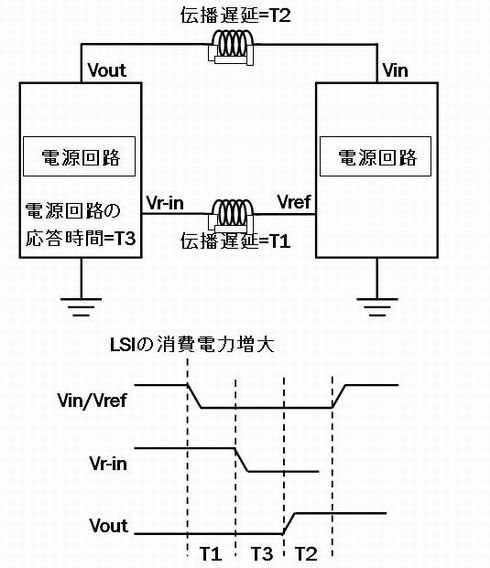

LSI内部に自分で電源回路をもてば、PDNの伝播時間をなくすことができますし、小さな回路ブロックごとに小さく応答の速い電源回路を作ることができます。高速応答の電源回路であれば、高速な回路ブロックの動作ON/OFFに対応して、電源のON/OFFをコントロールできます(図12)。

また、細かい回路ブロックごとに電源回路をもてば、小さな消費電流変化に対してもより細かい省エネが行えます。

基板上のバイパスコンデンサ削減はコスト、基板設計、消費電力と大きな効果があります。

Haswellではまだどの程度の電源回路がICの中に実装されるかは判明していません。しかし、これがICの消費電力やPIに対する回答の第一歩になることを期待します。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫前田真一の最新実装技術あれこれ塾

第21回 装置の電源

第21回 装置の電源

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第21回は、消費電力へのさまざまな要求が高まる中で注目されてきた「装置の電源」について解説する。 第20回 部品の内層実装

第20回 部品の内層実装

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第20回は、日本が伝統的に世界で優位に立っている実装技術「部品内装基板」について解説する。 第19回 CADデータの統合とPLM

第19回 CADデータの統合とPLM

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第19回は、協調設計とCADデータの重要性や、設計を並行して進めるコンカレントエンジニアリング、PDMとPLMなどについて解説する。