第11回 LSI消費電力把握の必要性と試み:前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第11回は、第10回に続き、LSIの消費電力についてさらに詳しく解説する。

3. 消費電力の把握

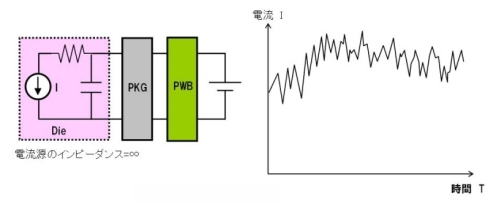

ICの消費電力を低減することは非常に重要なテーマで、多くの努力が進められています。EDAツールもICの消費電力を低減させる設計を行うための機能を次々とサポートしてきています。また、協調設計のためにICの消費電力を定義する方法としては、SPICEシミュレータで使われる電流モデルと呼ばれる方法が良いだろうということで、認識されています(図12)。

それに対して、ただ消費電力を下げるだけではなく、正確なICの消費電力の把握することに関しては、ツールや提案はあるのですが、なかなか困難で、これといった最適解がいまだに示されていません。

現在の提案では、例えば、膨大な解析時間が掛かったり、多くのIPをまとめたASICではインフラが整っていないため、情報の入手が困難であったりします。

このように、低電力化、電流モデルの形式は進歩があるのですが、モデルの基となるICの消費電力を設計時点で把握する手法の確立がなかなかできていません。

CPUやメモリは動作が比較的単純なので、消費電力の把握はASICに比べれば、簡単といえます。それでもMPUなどはソフトによって、メモリアクセスの多い場合や、整数演算が多い場合、フローティング計算が多い場合などで負荷が変化し、消費電力に大きな差が出ます。ただ、これらのCPUに対しては、高負荷で、同じ命令を連続で実行するベンチマークソフトがいくつか開発されているので、それらのテストを実行して最大消費電力を測定することが可能です。また、メモリやCPUは汎用品として設計開発を行うので、試作期間も長く、実チップを使って消費電力を測定することが可能です。システムICではこの消費電力の正確な把握が難しくなります。

まず始めに開発期間の問題があります。システムICはシステムにあわせて設計、製造するために、CPUやメモリなどの汎用ICよりも短い開発期間が要求されます。特に消費電力測定のためのテストベンチ的なソフトを開発したり、測定用治具を作成したりする時間とコストの余裕がない場合も多くあります。

また、システムICでは、多くのIPブロックを組み合わせて設計しますが、普通、IPは設計データや論理解析用モデルデータ、最大消費電力データなどはそろっていますが、詳細な内部情報は各社の知的所有権となり、情報開示はされません。

一般にシステムICの動作は、スマートフォンの動作でも紹介しましたように、全てのIPブロックが100%の稼働率で同時に動作することはありません。各IPの最大消費電力を単純に加算した場合、ASICの消費電力は膨大なものとなり、このままシステムの設計を行えば、過剰設計になってしまいます。

システムICの正確な消費電力をどのように把握するか、これは、システムの最適設計を行ううえで、必要な条件ですが、現実には困難な課題となっています。

誰もが必要性は分かっているのですが、実現には多くのコスト(解析時間)が掛かり、その情報を上手く使いこなすだけのインフラが無い状況です。

消費電流のモデルを作る方にも、使う方にもコストが必要ですが、現在は、そこにコストが掛けられません。『少ない需要に対してコストは掛けられない』、『モデルがないシミュレータに投資しても無駄だ』と、ここでも、鶏と卵の状態が起きています。

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

第10回 LSIの消費電力

第10回 LSIの消費電力

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第10回は、モバイル機器向けでは特に重視される、MPUやシステムLSIの消費電力について解説します。 第9回 TSVを前提としたモバイルDDR

第9回 TSVを前提としたモバイルDDR

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第9回は、モバイルDDRメモリの最新規格である、LPDDR3と、第3回で取り上げたTSVによって実現可能になったWide IOについて解説します。