戞9夞 TSV傪慜採偲偟偨儌僶僀儖DDR丗慜揷恀堦偺嵟怴幚憰媄弍偁傟偙傟弇乮2/3 儁乕僕乯

幚憰暘栰偺嵟怴媄弍傪暘偐傝傗偡偔徯夘偡傞慜揷恀堦巵偺楢嵹乽嵟怴幚憰媄弍偁傟偙傟弇乿丅戞9夞偼丄儌僶僀儖DDR儊儌儕偺嵟怴婯奿偱偁傞丄LPDDR3偲丄戞3夞偱庢傝忋偘偨TSV偵傛偭偰幚尰壜擻偵側偭偨Wide IO偵偮偄偰夝愢偟傑偡丅

3. LPDDR3

丂偙傟傑偱偺JEDEC偺儌僶僀儖儊儌儕婯奿偺柤徧偑LPDDR丄LPDDR2偲偁偭偨傛偆偵丄偙偺LPDDR3婯奿偼偙傟傑偱偺婯奿傪婎偵僗僺乕僪傾僢僾傪恾偭偨傕偺偱偡丅

丂JEDEC偵傛傞堦斒偺DDR儊儌儕婯奿偵DDR2偲DDR3偑偁傝傑偡丅LPDDR2婯奿偼DDR2婯奿傪婎偵丄儌僶僀儖梡婯奿偲偟傑偟偨偑丄LPDDR3婯奿偼DDR3婯奿傪婎偵偟偨傕偺偱偼側偔丄DDR2婯奿傪婎偵偟偨丄LPDDR2婯奿偺崅懍斉偱偡丅

丂偙偙偱丄昞1偵DDR丄DDR2丄DDR3偺婯奿偲LPDDR丄LPDDR2丄LPDDR3婯奿偺奣棯傪傑偲傔傑偡丅昞偵偼嵼傝傑偣傫偑丄梕検傕LPDDR3偼LPDDR2偺2攞傑偱懳墳偟偰偄傑偡丅

丂LPDDR3婯奿偼扨側傞LPDDR2婯奿偺懍搙傪忋偘偨偩偗偺婯奿偵側偭偰偄傞偺偼丄媫偒傚丄娫偵崌傢偣偱嶌傜傟偨婯奿偩偐傜偱偡丅

丂杮棃丄JEDEC偱偼丄師偺儌僶僀儖儊儌儕偵偼怴偟偄媄弍傪巊偭偰丄崅懍壔偲掅揹椡壔傪旘桇揑偵悇偟恑傔傛偆偲偟偰偄傑偟偨丅

丂偟偐偟丄偙傟傑偱偺惢昳偺墑挿偱偁傞丄実懷揹榖傗僨傿僕僇儊丄実懷壒妝婡婍偱偼側偔丄僗儅乕僩僼僅儞傗僞僽儗僢僩抂枛偺傛偆側怴偟偄実懷婡婍偑媫懍偵晛媦偟偰偒傑偟偨丅偙傟傑偱偺婡婍偺敪払偱偁傟偽丄怴偟偄儌僶僀儖儊儌儕婯奿偺惂掕傑偱偼丄LPDDR2婯奿偱娫偵崌偆偲巚傢傟偰偄偨傕偺偑丄怴偟偔弌尰偟偨婡婍偵懳偟偰偼丄LPDDR2婯奿偱偼丄婡擻晄懌偱丄怴偟偄儌僶僀儖儊儌儕婯奿偺惂掕傪懸偭偰偄偨偺偱偼丄娫偵崌傢側偔側偭偰偟傑偭偨偺偱偡丅

丂偙偺偨傔丄媫偒傚丄偡偖偵惢昳壔偱偒傞媄弍傪巊偭偰丄儊儌儕偺崅懍壔傪庡側栚昗偵丄徚旓揹椡偼憹偊側偗傟偽椙偄偲偄偆丄LPDDR3婯奿傪憗媫偵寛傔傞昁梫偵敆傜傟偨偺偱偡丅

丂LPDDR3婯奿偼棃擭乮曇拲丗2012擭乯拞偵偼婯奿傕寛傑傝丄婯奿偵懳墳偟偨儊儌儕傕弌尰偡傞偲婜懸偝傟偰偄傑偡丅

4. 敪憐偺揮姺

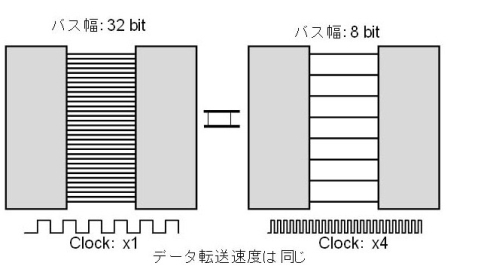

丂儊儌儕僶僗傪娷傔偰丄僶僗偺僨乕僞揮憲懍搙偼丄1儔僀儞摉偨傝偺揮憲懍搙偲僶僗偺僨乕僞暆偺愊偵側傝傑偡乮恾2乯丅

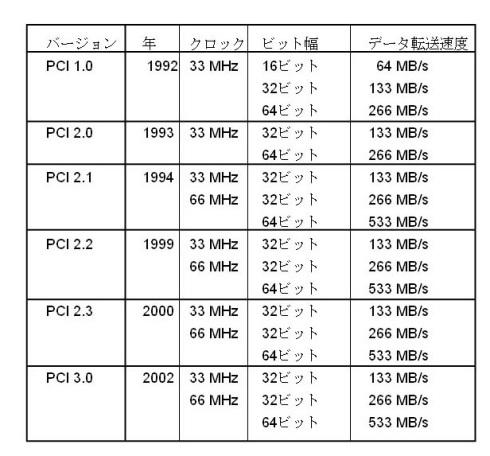

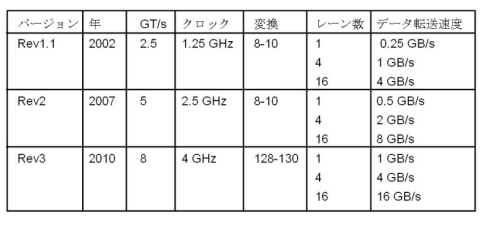

丂偙偺偨傔丄PCI僶僗側偳偱偼丄僶僗偺僋儘僢僋懍搙傪忋偘傞偲摨帪偵僶僗偺價僢僩悢傪憹傗偟偰僨乕僞揮憲懍搙傪忋偘偰偒傑偟偨乮昞2乯丅

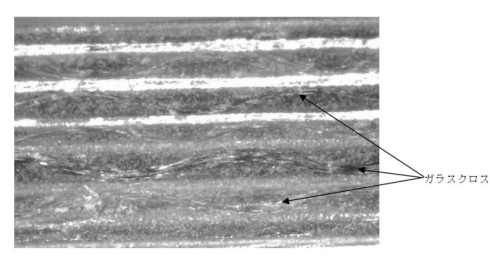

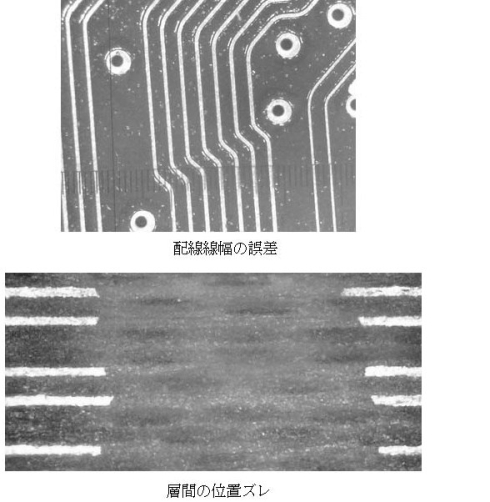

丂偟偐偟丄僋儘僢僋懍搙偺忋徃偵廬偭偰丄懡偔偺價僢僩僨乕僞偺摨婜偑崲擄偵側偭偰棃傑偟偨丅摿偵挿偄婎斅攝慄偱偼丄僋儘僗僩乕僋僲僀僘傗ISI僲僀僘丄婎斅偺僈儔僗慇堐偺傓傜乮恾3乯傗惢憿岆嵎乮恾4乯偵傛傞揱攄抶墑岆嵎側偳丄懡偔偺梫場偵傛傝丄慡偔摨偠攝慄挿偱偁偭偰傕僨乕僞儔僀儞娫偱敪惗偡傞抶墑岆嵎偑惂屼偟偒傟側偔側傝傑偟偨乮恾5乯丅

丂偙偺偨傔丄敪憐偺揮姺偑峴傢傟丄僶僗偺價僢僩暆傪1價僢僩偵偟偰丄僋儘僢僋懍搙傪忋偘偰丄僨乕僞揮憲懍搙傪忋偘傞僔儕傾儖僨乕僞揮憲偑搊応偟傑偟偨丅偦偟偰丄偙偺僔儕傾儖僨乕僞揮憲儔僀儞傪暋悢丄愝偗偰僨乕僞揮憲懍搙傪忋偘傞偲偄偆傕偺偱偡丅偍屳偄偺僔儕傾儖僨乕僞揮憲儔僀儞娫偱偼僨乕僞偺摨婜偼昁梫偁傝傑偣傫丅

丂暲楍偺PCI僶僗偐傜捈楍偺PCI Express僶僗偵側傝丄僨乕僞揮憲懍搙偑媫寖偵崅懍壔偝傟傑偟偨乮昞3乯丅

Copyright © ITmedia, Inc. All Rights Reserved.