第5回 光と銅:前田真一の最新実装技術あれこれ塾(2/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第5回は、光インタフェースと、銅を使う電気インタフェースのメリットとデメリットについて紹介する。

3. 光のコストと性能

それでは、なぜ光のコストは銅よりも高いのでしょう。

IntelとAppleが光の規格を銅も使えるように変更して、銅を採用したことからも、10Gbps(5GHz)以下の信号速度に対しては、銅の方がコストは安くなっていることは用意に分かります。

光で信号を伝達するためには3つの部品が必要で、これが現状では、銅に比べてコストが高い要因となっています。

- 電気⇔光変換

- コネクタ

- ケーブル

この3つです。

(1)電気⇔光変換

IC内部での信号処理や並列データ転送はすべて電気信号で行われています。これを素子間、基板間、装置間での高速データ転送に光を使う場合にはいったん電気信号を光に変換して、光ケーブルを介して送る必要があります。信号のレシーバ側では光信号を電気信号に再変換して、電子回路で処理を行います。

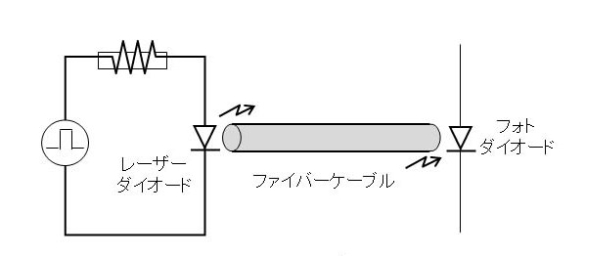

一般に『電気→光』変換にはレーザダイオード、『光→電気』変換にはフォトダイオードが使われます(図2)。

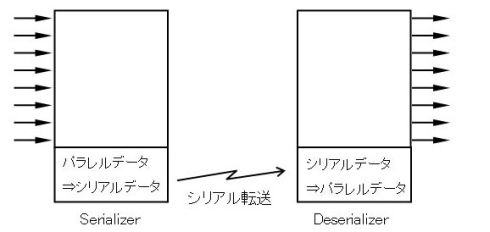

PCI Expressのような高速シリアルリンクでも8(128)ビット並列信号をデータ変換して10(130)ビットのシリアルデータに変換する必要があります。レシーバ側でも逆にシリアルデータをパラレルデータに逆変換する回路が必要です。この『シリアル⇔パラレル』変換をSer-Des (Serializer / Deserializer)と呼びます(図3)。

電気⇔光変換回路もSer-Des回路も同じ電子回路によって並列信号⇔直列信号変換しています。

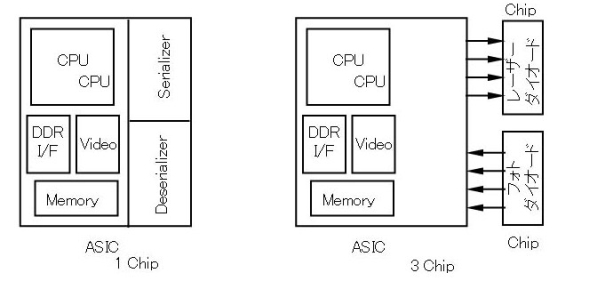

Ser-Des回路と、電気⇔光変換回路の大きな違いは光素子(レーザダイオード、フォトダイオード)が一般のICとは異なる構造であるため、SiPが出来ない点です(図4)。

Ser-Des回路は一般の回路ですので、IPとして多くの設計が流通していて多くのASICに組み込まれています。それに対して、光素子はCMOS ICと材質やプロセスが異なるため、同一ICチップに論路素子と光素子を一体化することが不可能です。論路素子と光素子を同一プロセスで作成し、同一チップに集積する研究もありますが、無理をしているため、コストや集積度、歩留まりなどで問題があり、現在は実用的ではありません。

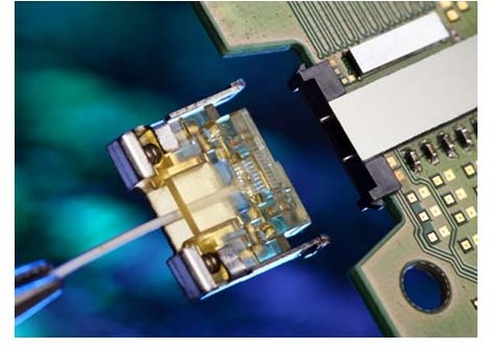

また、Intelを始め多くの会社が光による信号伝送モジュールやシステムを発表しています。ショーや学会では常に光関係のデモ、発表は行われています。研究は進んでいると思われますが、まだ銅との競争力がないのか、量産製品化は行われていません(図5)。

Ser-Des回路はASICのコストだけで済みますが、光素子ではASICとは別チップにする必要があるので、光素子分のコストが上昇します。しかも光素子といっても、レーザダイオードとフォトダイオードもチップを分ける必要があります。

もちろん、部品が別になりますから、基板上の実装面積も大きくなります。次のコネクタの項でも説明しますが、光素子にはそのまま光ケーブルを接続する必要があるので、レーザダイオードもフォトダイオードもある程度の大きさが必要で、実装面積の増大も超小型機器では無視できない程度になります。

これは、コストアップとともに小さいことが要求される機器では、性能のダウンになります。

光が使われるようになるためには論理回路と光ドライバ、レシーバがSiP化できることが必要とされます。このため、先に紹介したIntelの例のように光素子をSi上に作る研究が各方面でなされています。

しかし、これとは異なる方法で、光素子と論理素子をSiP化しようとするアプローチもあります。

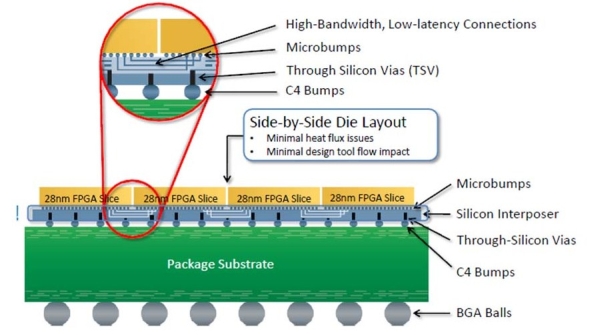

これは以前紹介したTSVを使ったMCMです(図6)。この方法であれば、まったくプロセスの異なる光素子とCMOS回路を同一パッケージに集積できます。

Xilinx社やAltera社など多くのASICベンダ光インタフェースを内蔵したパッケージや IPを今後サポートしてゆくとアナウンスしています(図7)。

Copyright © ITmedia, Inc. All Rights Reserved.