進化する開発環境が一堂に――設計開発者の羅針盤「EDS Fair 2012」:EDS Fair 2012(2/2 ページ)

設計ソリューションの必須技術を網羅する展示会「EDS Fair 2012」がパシフィコ横浜で開催。「バーチャル・プロトタイプ」や「ESL」など最新の開発環境が紹介された。

システムレベルでモデリング

メンター・グラフィックスは、「オートモーティブ」をテーマに、会場でさまざまな自動車向けソリューションを紹介した。特に、設計の抽象度を上げたシステムレベルのモデリング作成機能、検証/解析機能などを提供するESLソリューション「Vista」を中心に、車両制御系/パワートレイン系に向けたバーチャル・プロトタイプ技術「SystemVision」、AUTOSAR4.0対応の車載システム設計ソリューション「Volcanaファミリ」などのデモ展示を行った。

「より高い抽象度のハードウェア・モデルを作成でき、その上でソフトウェアの開発と検証を行えるのが強み。バーチャル・プロトタイプによる開発環境は、自動車業界に加えてデジタルカメラの開発などにも利用されている」(説明員)という。

Vista(画像3)は、SystemC TLM2.0対応モデルの作成を支援したり、ソースコードのデバッグや検証、作成したモデルの性能解析を行ったりすることができるソリューションである。ハードウェア開発環境「Catapult」と連携すれば、ANSI C/C++からRTLを自動生成することができる。設計の抽象度が高いバーチャル・プロトタイプからの高位合成を可能にすることで、ハードウェア実装に関わる生産性は従来に比べて20倍に向上するという。また、ソフトウェア開発環境「Sourcery CodeBench」と連携すれば、さまざまなプロセッサとOSに対応する組み込みソフトウェアを生成することができる。Sourcery CodeBenchでは、新たにQualcomm Technologies社の「Hexagon DSPアーキテクチャ」のコード生成をサポートすることも発表された。Hexagon DSPは、Qualcomm Snapdragonプロセッサに複数個搭載されているという。

マルチフィジックスソリューションを実現する操作環境

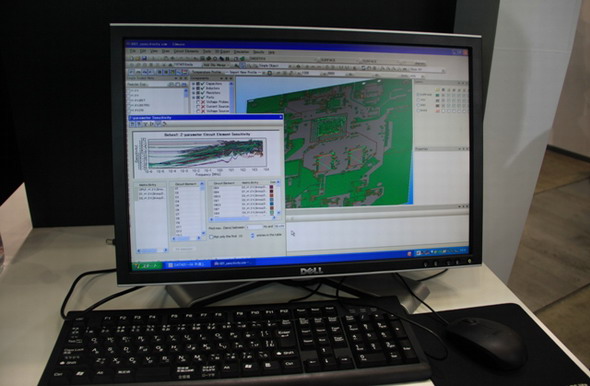

アンシス・ジャパンは、チップ〜パッケージ〜システムの協調設計を支えるシミュレーション環境を提供している。特に、アパッチ社が2011年に同社の100%子会社となり、チップ内部のシミュレーション環境が新たに拡充された。会場では、信号品質や電力品質から熱の解析まで、アパッチ製品との連成によるさまざまなソリューションが紹介された(画像4)。

アンシスは、1つのテーマとして「シミュレーション主導の製品開発(SDPD:Simulation Driven Product Development)」を掲げている。企業(顧客)が開発の早い段階で多くの設計案を分析して、技術革新を促すために必要となる時間とコストを最小限に抑えることができるようにするためだ。同社はエレクトロニクス関連の設計環境として、以前からパッケージやボードレベルのシミュレーション環境を提供してきた。新たにアパッチ社の製品群を加えたことで、チップレベルの信号品質の解析などまでサポートの対象範囲を広げた。

アンシスの強みは、マルチフィジックスソリューションを実現する操作環境「ANSYS Workbench」を提供していることだ。モデリングからメッシュ生成、さらには構造、磁場、流体などの解析機能、評価まで、一連の作業を統一した環境で実行できる。「Workbenchを介して、解析に関わる全てのプロセスを1つにつなぐことができる。このため、電磁解析した電力品質などのデータを熱解析にも容易に利用できる。構造や流体振動、伝熱、音響、落下衝突など、さまざまな分野の解析をサポートしているツールベンダーは少ない」(説明員)という。

システムレベル記述からハードウェア実装を実現

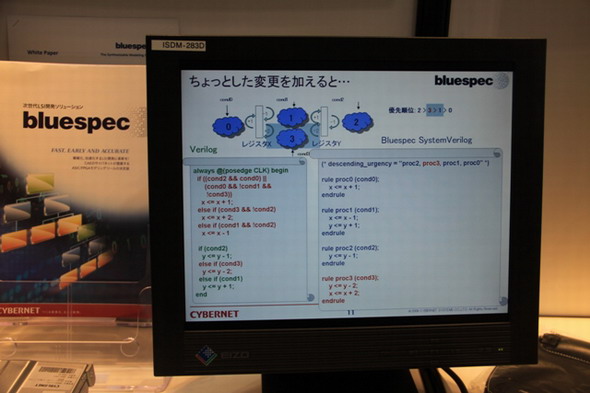

サイバネットシステムのブースで、来場者の注目を集めていたのがBluespec社の高位合成ソリューションである。製品が高機能かつ高性能となるにつれ、電子回路が大規模となりシステム開発は複雑になってくる。このため、LSIの開発工程において、設計の抽象度を従来のRTLからシステムレベルに引き上げていこうという動きは早くからあった。しかしながら、これまで提案されてきた多くの設計手法では、制御系の回路などをハードウェア化するにあたって、設計者の意図を詳細に反映することが煩雑になることもあり、システムレベル設計がなかなか浸透しなかった経緯がある。

Bluespec社が提供している記述言語「Bluespec System Verilog(BSV)」は、MIT(Massachusetts Institute of Technology)で開発された言語で、RTLよりも設計の抽象度が高く、完全な並列性を表現することができるのが特徴だ(画像5)。

仕様書に基づきBSVで記述された機能モデルは、Bluespecコンパイラを用いて、論理合成可能なverilog RTLと検証用モデル用のSystemCを自動生成することができる。「BSVの設計環境では、論理回路などマイクロアーキテクチャの設計は、さまざまな経験と知識を生かして技術者が行う。これに対して、並列性の管理や競合の排他制御のプログラム記述は、差異化が難しくケアレスミスなどエラーが発生しやすいため、ツールに任せコンパイラが自動生成する」(説明員)と述べた。さらに「これまで提唱されてきたシステムレベル設計の記述言語はCがベース。BSVはハードウェア設計者にもなじみのある記述言語なので、比較的取り組みやすいのではないか」と続けた。

Copyright © ITmedia, Inc. All Rights Reserved.