第3回 TSVがもたらす新しいMCM:前田真一の最新実装技術あれこれ塾(3/3 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第3回は、パッケージ内でメモリチップを積層するためのキーテクノロジとして注目されている「TSV」について紹介する。

3. MCM

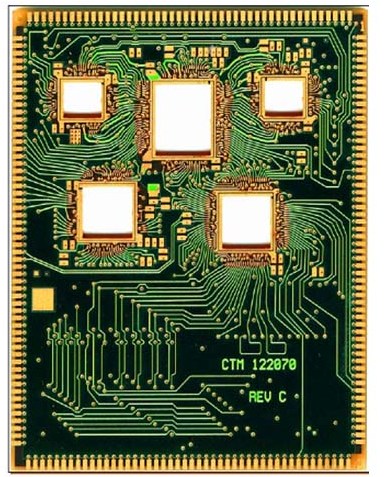

MCM(Multi Chip Module)は複数のダイをパッケージ内で接続してSiP(System in Package)としたものです(図12)。SiPやハイブリッドIC、MIC(Microwave IC)の明確な定義上の区分けはありませんが、ICパッケージよりもよりも少し大きめのモジュールとなっていて、デジタル回路システムが組まれている形態を主にさしています。複数のダイを1パッケージに実装していてもDDRメモリのスタックド実装はシステムではないので、MCMとは呼びません。

現在、ICは配線の微細化が進み、1チップに集積できる回路規模が飛躍的に大きくなってきています。ダイは小さいほど歩留まりは高くなりますが、複数のプロセッサを同一のダイに搭載することにより、プロセッサ間のデータ受け渡しを高速化したり、プロセッサ間の接続をダイナミックに変化させたりすることにより、チップ性能を向上させているのです。プロセッサごとに異なるICに分割したのでは、部品ピン数も多くなり、処理能力も低下します。大きなダイサイズになってもマルチプロセッサの1チップ化は効果があるのです。システムICでも、ダイサイズの巨大化の問題はあります。

回路規模を大きくしようとすれば、当然大サイズは大きくなります。また、ここでも回路の並列化の問題は生じます。例えば16ビットのデータ処理回路を並列にして32ビットにしたり、4つ並列にして64ビット並列処理をしたりということは良く行われます(図13)。

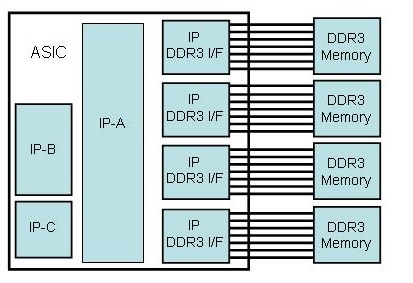

IPを使った設計は開発期間を短縮し、動作も保証されているため、大規模ASICの設計には非常に有用で、不可欠な要素です。しかし、ASICの設計のためには無駄が生じていることも確かです。

IPはASICの設計効率を高めるため、多くのライブラリを用意しています。例えば、同じ動作をする回路に対して、3層レイアウトと4層レイアウトを用意し、他のIPと同じ層数で回路が実現できるようにしているIPも多くあります。

多くのIPを使って大きなシステムICを設計するときは、最も層数の大きなIPの層数で、最も微細な加工をするIPの設計規則でチップを設計、製造する必要があります。このような大規模LSIでは、無理にSoCとせずに小さな最適設計チップに分割してMCM化した方が効率が良いのではないかとの考えが出てきました。

また、センサやパワー回路、高周波回路など、他のチップとは異なるテクノロジで作成したり、他の回路と別のチップにしたい回路など、このような複数のチップを1パッケージに集積する場合などMCM構造とします。

MCMでは、基板を介しての配線が信号の品質を落としたり、チップ内の多くの配線を基板で配線する困難さなどから、どうしても1チップでシステムを実現するSoCよりもパフォーマンスが低下してしまいます。

また、チップの実装、基板の信頼性、基板とチップの熱膨張率の違いによる熱応力など、SoCより、歩留まり、コストが上がってしまっていました。

しかし、今後、安価で高信頼性のTSVが実用化されると、TSVを使ったシリコン基板が、MCMに使えるようになります。大きなダイのSoCを使うより、最適設計した小さなIPブロックや、CPUモジュールを組み合わせMCMで最適システムを構成した方が効率が良くなるのではないかとのアプローチが出ています。

4. TSVを使ったMCM

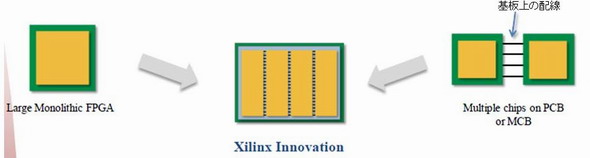

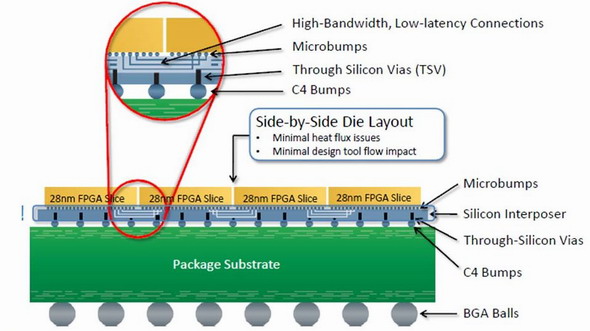

Xilinx社が昨年の10月にスタックドシリコン インターコネクト テクノロジと呼ぶ、TSVを使ったMCM製品を発表しました。今年のDesignConでそのTSVの電気特性を発表しています(※1)。それについて簡単に紹介します。

Xilinx社の発表では、ダイの面積と歩留まりの関係を述べていますが、特に新しい微細テクノロジに移行した場合、生産初期の歩留まりの問題を挙げています。できるだけダイ面積を小さくして歩留まりを上げたくても、一般の基板をインタポーザとして使ったMCM-Lではパフォーマンスが確保できません。その解決として、TSVを使ったシリコン基板を使ったMCM-Dを使うことにより、電気性能やサイズは1チップのSoCと同等を保ちながら、チップの歩留まりを大きく向上できると提案しています(図14)。

発表では、MCM-LからMCM-Dにすることにより、ワット当たりダイ間帯域幅は100倍以上になったといっています。これは、単に速度比ではなく、配線が短く、配線特性が良くなったことにより、ドライバの出力が小さくできるようになったことの相乗効果によるものです。

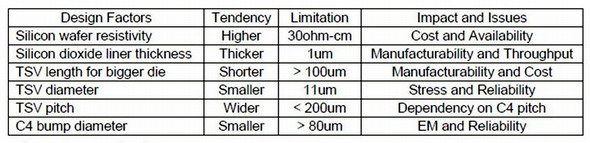

TSVを使ったシリコン基板配線の特性がSoCでのチップ内でのIP間配線の特性と比べ、パフォーマンス的にそれほど大きな違いがないことを確認する必要があります。そのためにTSVをシミュレータでモデル化すると同時にテスト基板(TEG=TestElement Group基板)を作成、実測とシミュレーション結果の一致を確認した論文です。

図15にXilinx社の考えるMCM構造、表1に、同論文より、今回のTSVの仕様を紹介します。なお、インタポーザの厚さは100um、配線幅は65nmとのことです。参考文献※1Namhoon Kim, Zhaoyin Daniel Wu, ArifRahman, Dongwook Kim, Paul Wu "ThroughSilicon Via (TSV) Design ConsideringTechnology Challenges for Very High-S peedSignal Transmission"2011DesignCon

筆者紹介

前田 真一(マエダ シンイチ)

KEI Systems、日本サーキット。日米で、高速システムの開発/解析コンサルティングを手掛ける。

近著:「現場の即戦力シリーズ 見てわかる高速回路のノイズ解析」(技術評論社)

Copyright © ITmedia, Inc. All Rights Reserved.