第1回 DDR4:前田真一の最新実装技術あれこれ塾(2/3 ページ)

「実装が新しい技術の普及を左右している――」。実装技術の専門誌「エレクトロニクス実装技術」で好評連載中の前田真一氏がMONOistに登場。実装分野の最新技術を分かりやすく紹介する。第1回のテーマは、次世代メモリ「DDR4」だ。

3. 低電力化とその必要性

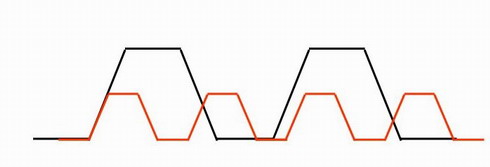

電源電圧が低下し信号の振幅が低下すると、それだけでICの高速化が実現できます(図2)。

また、電源電圧の低下はICの消費電力を低減させます。もし、ICのインピーダンスZが一定だとすると、ICの消費電力Wは、電源電圧VとZで表すと、

W=(V×V)/Z

となります。

Zが同じならば、Vの2乗で電圧低下がWの低下になります。

はじめのSamsungの発表では、今回のDDR4メモリの消費電力は従来のDDR3メモリから半分に低電力化した、としています。

電源電圧が1.5Vから1.2Vに低下すると、2乗で約1/1.5(36%)の消費電力の低下となります。発表では40%の削減になったと書いていますが、これはICのインピーダンスZが増大したことを意味します。これはSamsungが今回のDDR4を30nmテクノロジーで作成したと書いてあることから納得できます。

現在のDDR3メモリは、45〜40nm程度で製造されています。配線が細くなれば抵抗は大きくなるので、30nmで作られるDDR4は電源電圧の低下とあわせてDDR3の40%の消費電力が達成できたのでしょう。この低電力化はDDR4メモリの大きなキーテクノロジーです。このため今回のプレスリリースでも特に強調されていました。

信号の高速化と共に、SSOによるICの電源供給ラインに発生するノイズ問題については、これまでの連載でも何度か触れてきました。

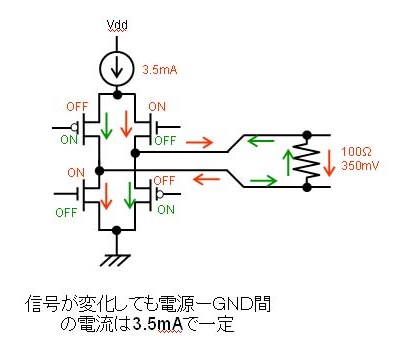

DDR4はパラレル信号バスのクロックがGHzになるのです。シリアルリンクに使われるLVDSテクノロジは、原理的にはドライバのスイッチングによるICの消費電流の変化は発生せず、SSO問題は発生しません(なお、実際にはそれ以外の理由で発生します)(図3)。

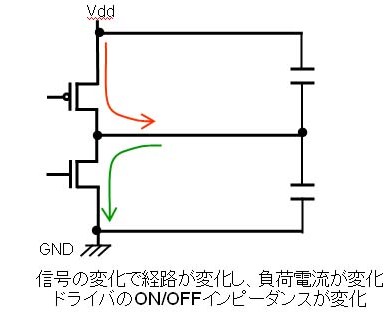

しかし、DDRメモリに使うCMOSテクノロジはSSOノイズが多く発生します(図4)。また、後で触れるように、コンピュータのメモリ使用量の急激な増大により、メモリがシステム内で使う電力も急激に増大します。このため、チップ1個の消費電力減少のための技術はそのままDDR4メモリの消費量につながる技術なのです。

4. 規格の互換性

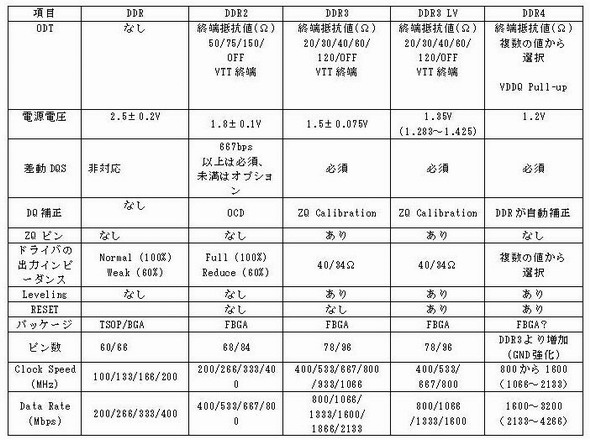

参考までに、表1に現在までのDDRメモリ規格にIBMの発表にある、現在、考えられるDDR4の機能を加えたものを示します。

これまでのDDRメモリ規格の変遷から見ると、データの転送速度が2倍になると同時に、いきなり大きな変化が導入されることもありませんでした。

たとえば、一見、大きな変化に見えることでも、その機能を使わなければ一つ前の規格の高速版として新しいメモリが使える程度の変化でした。

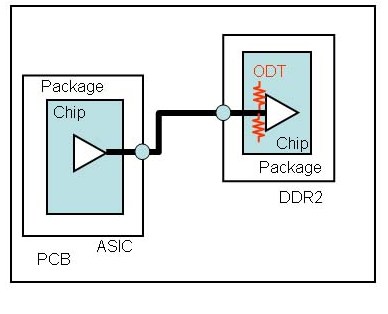

DDRメモリからDDR2メモリでの大きな違いは、DDR2でODTという機能が追加されたことでした。これは、終端抵抗をIC回路に内蔵してしまい、基板上で終端抵抗を付加しなくて良い機能です(図5)。しかもIC内部の終端抵抗は何種類かの値が用意されていて、最適な抵抗値が選べる機能です。

しかしこの機能はオプション機能で、IC内部の終端抵抗を使わなければ、以前のDDRと同じように基板上で終端勝利を行っても問題ありませんでした。

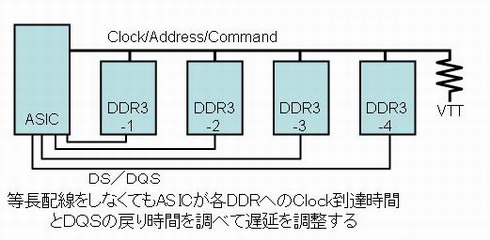

DDR2からDDR3への変更の時もそうでした。DDR3でタイミング調整をしてくれるレベリングと呼ばれる機能(図6)も、やはり使わなければDDR2と同様になる機能でした。

これは、現在のDDRメモリは非常に高度な機能をもっていて、メモリを接続するメモリコントローラ自身がMPUを使ってDDRメモリを細かくコントロールする必要があるからです。高速信号を基板上に実装する際に生じる伝送線路上の多くの問題、波形変化やタイミングの誤差などをできるだけコントローラが補正し、基板への実装を楽にするように考えています。

IC内部の終端抵抗値の設定や、タイミング誤差をコントローラが自動的に補正する機能など、コントローラ内部のソフト、ハードの機能は決して小さなものではありません。

メモリの規格が新しく決まってから、できるだけ早く新しい規格のメモリが出現し、普及して欲しい時、新しい規格を全てサポートするメモリコントローラの出現を待つのではなく、古い規格のメモリコントローラでも新しい規格のメモリが使えるようにするため、新しいメモリ規格は、古いメモリ規格と互換性をもたせます。

こうすれば、電源電圧を変更するだけで簡単に古いメモリコントローラで高速・低消費電力の新しいメモリが使えるようになります。

Copyright © ITmedia, Inc. All Rights Reserved.