USB 3.0の概要:USB 3.0、スーパースピードを支える技術(1)(2/2 ページ)

高速な次世代インターフェイスとして注目されるUSB 3.0の新連載。第1回はUSB 3.0の最新動向や技術概要、仕様などを紹介

そこで、今回と次回の2回にわたってUSB 3.0の物理層の概要を解説していこうと考えています。とはいえ、こうした技術の多くの部分はSerial ATAやPCI Expressなどの高速インターフェイスと共通している技術でもありますので、USB 3.0スーパースピードの物理層を勉強すると、ほかのインターフェイスの物理層も比較的簡単に理解することができます。あるいは、Serial ATAやPCI Expressを勉強された方には、比較的理解が早いものと期待しています。

このように大きく異なる物理層を持つUSB 3.0スーパースピードですが、最も広範に普及したUSB 2.0の資産を最大限に活用するため、上位のプロトコル層では多くの部分でUSB 2.0を継承しており、アプリケーション層においては既存のクラスドライバをそのまま使います。このように大きく異なる物理層と大きな変更がないプロトコル層とのギャップを解消するため、新たにリンク層が追加され、パケットのフレーミング、リンクの確立などを担当しています。また5Gbits/sの超高速リンクを維持するには電力が必要なので、より効率的な通信が行えるような工夫が施されています。

その1つが、ユニキャストと呼ばれる通信方式です。USB 2.0ではホストが通信を開始する際に、接続された全デバイスに対して一斉送信をするブロードキャストが用いられていましたが、USB 3.0スーパースピードでは、特定のデバイスにだけ送信するユニキャスト方式が採用されています。

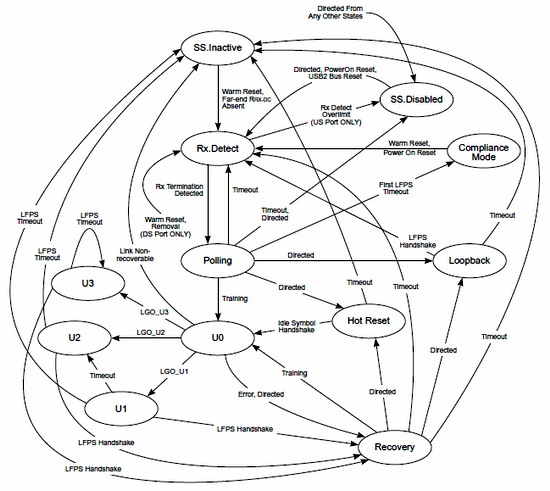

また、USB 3.0スーパースピードにおいては、図6のLink Training and Status State Machineでも示されているように、U0/U1/U2/U3の4つの電力状態を切り替える、きめ細かなパワーマネジメントが行えるようになっています。USB 3.0スーパースピードを理解するには、物理層とリンク層の理解が重要となりますので、本連載では物理層の解説の後、プロトコル層の解説の中でリンク層の説明を多く盛り込もうと考えています。

最後に、不足しがちなバスパワーの電力が500mAから900mAに引き上げられていたり、デバイス側から電力が供給できるパワードBコネクタも規定されているように、USB 3.0では、高速伝送のみならず使い勝手も向上しています。

関連した仕様

USB 3.0自体の仕様は、ご存じのようにUSB-IFから2008年11月にリリースされた「Universal Serial Bus 3.0 Specification Revision 1.0」(図7)で規定されていますが、ホストコントローラに関しては、USB 2.0で用いられていたPCIベースのEHCI(Enhanced Host Controller Interface)に代わり、PCI ExpressベースのxHCI(eXtensible Host Controller Interface)へ変更となっています。

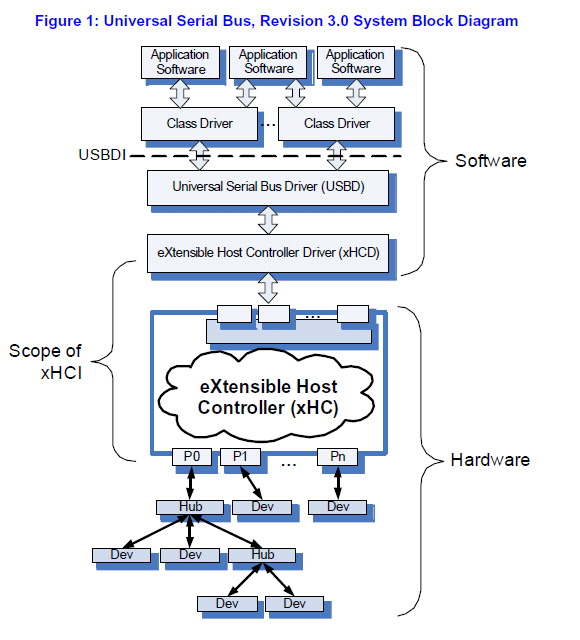

このxHCIのSpecificationは、2010年3月25日現在でRevision 0.95(図8)とまだ正式版には至っていませんが、図9のアーキテクチャ図で「Scope of xHCI」と示された部分が規定されており、主要な機能として、

- USB 3.0のサポート

- 従来のUSB 2.0およびUSB 1.1のサポート

- パワーマネジメントのサポート

- 従来のUSBホストコントローラの問題の解決

- メモリアクセスの最適化

- ハードウェアの簡素化

- 32bitおよび64bitアドレスのサポート

- バーチャルメモリのサポート

- バーチャライゼーションのサポート

などが記述されています。ただ、これらの詳細を紹介するのは本連載の目的ではありません。今回は、EHCIのSpecificationが155ページであるのと比較して、xHCIのSpecificationが0.95の段階で414ページと約2.7倍もの量になっていることをお伝えします。

xHCIのSpecificationの詳細についてご興味のある方は、Intelのサイトから入手してご確認ください。ただし、0.95のリビジョン(改訂番号)が示すように、まだDraftの状態なので正式には公開されていません。Intelと契約(xHCI SPECIFICATION CONTRIBUTOR AGREEMENT)を結んで、正式バージョンへ向けた協力を前提としたうえで配布されるようになっています。

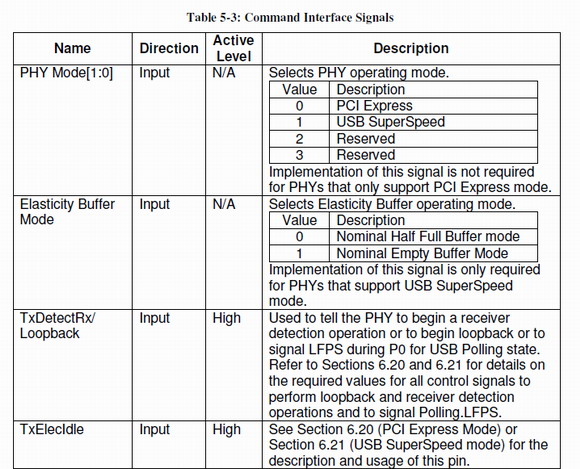

また、物理層のインターフェイスに関しては、「PHY Interface For the PCI Express* and USB 3.0 Architectures Version 3.0」(図10)に記載されています。このドキュメントは、Intelのサイトから自由にダウンロードすることができます。表紙にもあるように、USB 3.0だけではなくPCI Expressとの併記という形を取っています。これは取りも直さず、USB 3.0の物理層がPCI Expressの資産を有効に使って開発されたことを如実に物語っています。

内容を見てみると、PCI Express ModeとUSB SuperSpeed Modeの2つのモードがサポートされており(図11を参照)、ここからもPCI Expressと転送速度を含め多くの技術的共通点を持つことが分かります。

しかしながら、基本的にパソコンの内部バスであるPCI Expressと、外部機器とのインターフェイスであるUSB 3.0では使用目的が大きく異なるので、その使用環境に合わせた独自の機能などが規定されています。次回からは、こうした機能を中心に解説していきます。

Copyright © ITmedia, Inc. All Rights Reserved.