低価格FPGAでも文字認識AIの学習は可能なのか:FPGAにニューラルネットワークを実装する(4)(2/2 ページ)

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第4回では、低価格FPGAである「Tang Nano 9K」ではこれまでうまくいかなかった文字認識AIの学習が可能になったので、その結果を紹介する。

学習ロジックに関するコード記述

30〜33行目は学習ロジックに関する記述となります。アルゴリズム自体は、連載第2回で紹介したC言語で示した学習モデルをそのままVerilogに書き換えた感じですので、その内容説明も同記事をご参照ください。ここでC言語で書いたコードと決定的に異なるのは、C言語でコンパイルしたコードはCPUで逐次実行されるのに対し、FPGAの場合は同じForループのように見えますが33行目の式は並列実行可能なロジックに展開される点です。

リスト1に挙げたコメントにはないのですが、このソースコードをリポジトリに更新する際に書いたコメントが以下のリスト3の通りです。

The learning logic was changed to nobloking assignment.

33行目ですが、今回のコードの改訂では学習データ(links)に値を代入する式をノンブロッキングに変更しました。これは、左側から右側への代入を“=”から“<=”に変えることで、ブロッキング代入からノンブロッキング代入に変更できるからです。

Verilogでは、for文で記述されたループ文はシンセサイザー(C言語でいうコンパイラのようなもの)でfor文の内側の33行目の式は、今回の場合ですと525行の式に展開されます。その式の代入をノンブロッキングに変更すると525行ある式が全て同時に実行されます。

これはFPGAを使う上で大きなメリットの一つなのです。これはC言語によるコードを用いるコンピュータではできない芸当ですよね。

使い方と実行

最後に、今回書いたコードの検証をFPGAの実機で試しておきましょう。

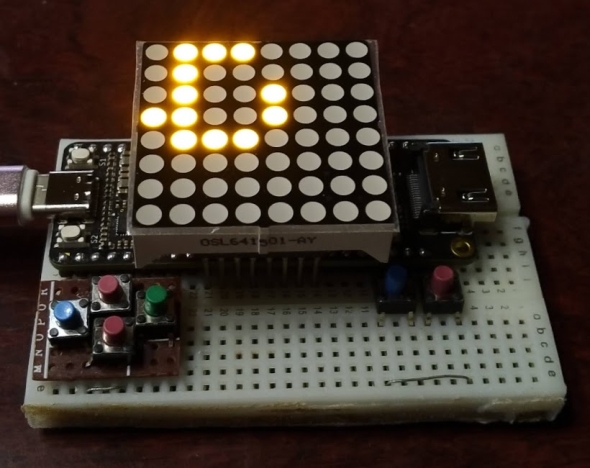

図1は、PCとつなげたFPGA開発環境からUSB経由で生成したビットストリームをFPGAにダウンロードして、図1の左側にあるUSBコネクター上側の白いタクトスイッチを押したときのものです。いわゆる検証用の入力サンプルですね。学習データの“D”を2カ所ほどドット改変しており、neuro.vの19行目で設定されたビット列をLEDドットマトリクスに表示しています。

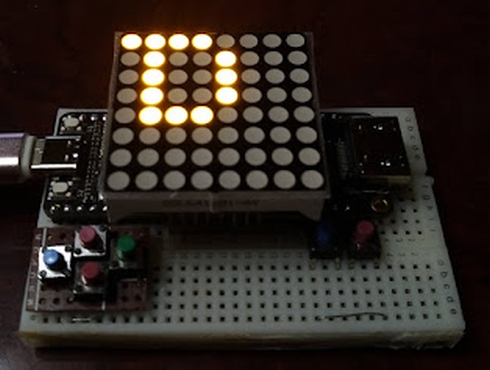

次の図2は先ほどのサンプル入力文字を推論させた結果です。きちんと学習で使った“D”に収束していますよね。

本連載の読者の皆さんはお気付きかもしれませんが、前回に比べてLEDドットマトリックスのLEDの色が黄色(アンバーかもしれない)に変わって、サイズも大きくなってませんか。いや実は、筆者の妻にこのデモを見せたところ「こっちが好き」という意見だったので、こちらを使うことにしました。

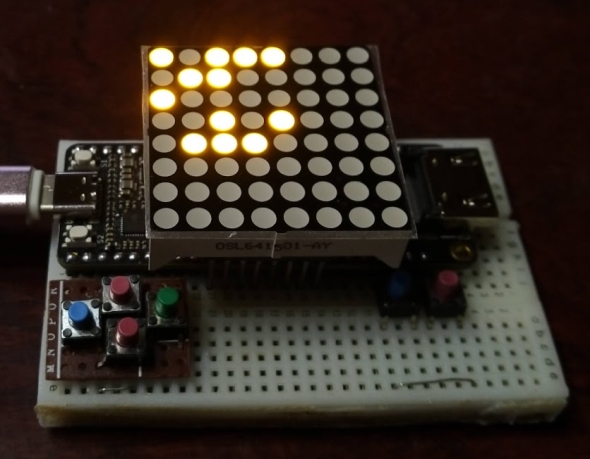

図3はランダムなビット列で入力文字を生成した例です。

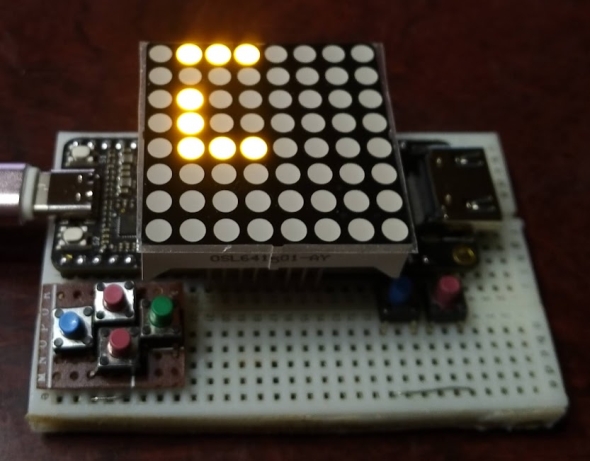

図4は、学習によって覚えさせた4文字のどれにも到達しなかった結果となる失敗例です。ですが、機械学習において推論が成功しなかったことが分かるか否かはとても重要な知見だと思っています。

おわりに

冒頭でも紹介した通り、今回も学習時のノイズ混入実験にトライしています。これは、ニューラルネットワークを基本とする深層学習において、ある種のノイズを用いてAIシステムに誤判断させるという敵対的手法の一つです。これらについては、今回の記事を執筆するまでに得られた知見ではそれを原稿に収めるところまでは至りませんでした。次回以降、進捗があれば紹介したいと思います。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫連載「FPGAにニューラルネットワークを実装する」バックナンバー

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

FPGAに学習済みニューラルネットワークを実装して推論を実行する

FPGAに学習済みニューラルネットワークを実装して推論を実行する

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第3回では、PC上で生成した学習済みニューラルネットワークをFPGAに実装して推論を実行する。 最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第2回では、ニューラルネットワークのモデルの一つである「ホップフィールドネットワーク」を用いて、PC上で文字認識を行えるようにする。 低価格FPGAを用いた文字認識AI推論の全体像

低価格FPGAを用いた文字認識AI推論の全体像

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第1回では、連載の狙いや、文字認識AIモデルの概要、どのようにFPGA上で文字認識を行うかなど全体の流れを紹介する。