連載

FPGAに学習済みニューラルネットワークを実装して推論を実行する:FPGAにニューラルネットワークを実装する(3)(3/3 ページ)

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第3回では、PC上で生成した学習済みニューラルネットワークをFPGAに実装して推論を実行する。

物理制約ファイル

物理制約ファイル(Physical Constraints File)とは、先に示したVerilogのモジュールの定義で設定した入出力ポートを実際のFPGAのピンに割り当てるファイルです。リスト4のneuro9k.vに対応する物理制約ファイルはリスト7のneuro9k.cstです。そのソースコードは、neuro9k.vと同じリポジトリにあります。

1: IO_LOC "clk" 52; 2: IO_LOC "rst" 4; 3: IO_LOC "btn[0]" 3; 4: IO_LOC "test2" 68; 5: IO_LOC "test1" 69; 6: IO_LOC "low" 81 7: 8: IO_LOC "col[0]" 74; 9: IO_LOC "col[1]" 34; 10: IO_LOC "col[2]" 40; 11: IO_LOC "col[3]" 71; 12: IO_LOC "col[4]" 41; 13: IO_LOC "col[5]" 72; 14: IO_LOC "col[6]" 76; 15: IO_LOC "col[7]" 77; 16: 17: IO_LOC "row[0]" 70; 18: IO_LOC "row[1]" 75; 19: IO_LOC "row[2]" 51; 20: IO_LOC "row[3]" 73; 21: IO_LOC "row[4]" 30; 22: IO_LOC "row[5]" 42; 23: IO_LOC "row[6]" 33; 24: IO_LOC "row[7]" 35;

リスト7 neuro9k.cstのソースコード

1行目の「IO_LOC "clk" 52;」を例にとると、Verilogで定義した"clk"を実装したいFPGAのピン番号“52”に割り当てています。

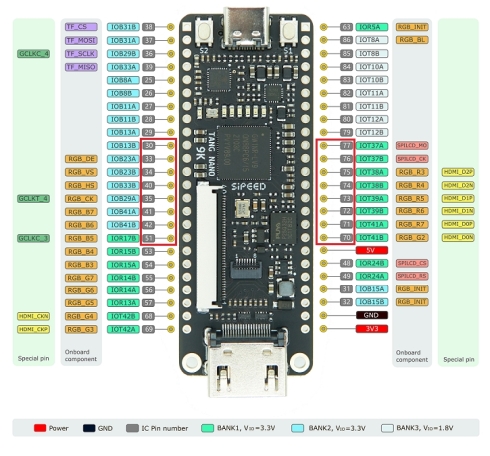

図1はTang Nano 9Kのピン配置を示します。赤枠で囲んだ部分のピンにLEDドットマトリクスが接続されます。また、基板の上側についているUSB-Cコネクターの両脇にある2つの白いボタンの内、右側にあるのがリセットボタン(rst)で、左側にあるボタンがbtn[0]になります。

FPGAに実装したニューラルネットワークで推論を実行する

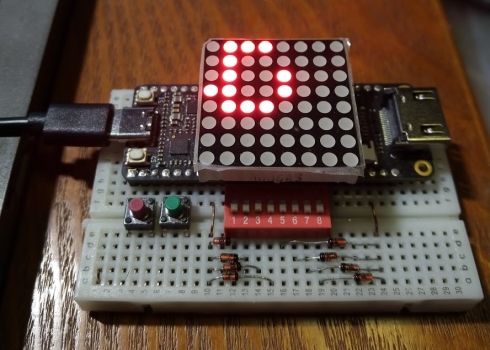

図2は、LEDドットマトリクスに推論させたい手書き文字を表示させたものです。

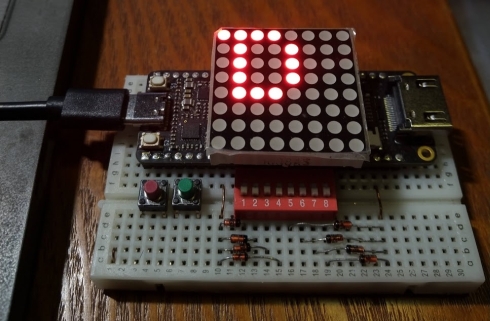

図3は推論した結果です。

FPGA上での推論の流れは本連載の第1回を御覧ください。

おわりに

いかがでしたでしょうか。次回はFPGA上での学習にチャレンジします。お楽しみに。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- ≫連載「FPGAにニューラルネットワークを実装する」バックナンバー

- ≫連載「オリジナルCPUでバイナリコード入門」バックナンバー

- ≫連載「注目デバイスで組み込み開発をアップグレード」バックナンバー

最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

最も古典的なニューラルネットワーク「ホップフィールドネットワーク」を学ぶ

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第2回では、ニューラルネットワークのモデルの一つである「ホップフィールドネットワーク」を用いて、PC上で文字認識を行えるようにする。 低価格FPGAを用いた文字認識AI推論の全体像

低価格FPGAを用いた文字認識AI推論の全体像

FPGAにニューラルネットワークを実装するプロセスを学ぶ本連載。第1回では、連載の狙いや、文字認識AIモデルの概要、どのようにFPGA上で文字認識を行うかなど全体の流れを紹介する。 新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

新たな教材となる「Tang Nano 9K」を使ってLEDマトリクスを制御する

オリジナル4ビットCPUを用いてバイナリコードを学ぶ本連載。第4回は、バイナリコーディングを学ぶための新たな教材となる「Tang Nano 9K」とVerilog-HDLコードを使ってLEDマトリクスを制御する。