Armのクライアント機器向け最新ソリューション「TCS23」の全貌:Arm最新動向報告(16)(2/3 ページ)

Armの最新動向について報告する本連載。今回は、2023年5月30日〜6月2日に開催された「COMPUTEX TAIPEI 2023」で発表されたクライアント機器向けの最新ソリューションである「TCS23」を構成する各IPを紹介する。

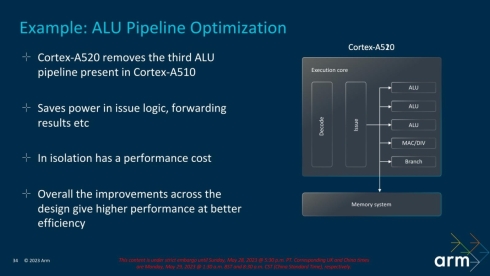

「Cortex-A520」はALU数を減らしながら性能を引き上げ

これをもっと極端にしたのがCortex-A520である。こちらはCortex-A510比で22%の性能/消費電力比向上であるが、内部のパイプラインでは、ALUを×3から×2に減らしている(図10)。もともとインオーダーのパイプラインだから、アウトオブオーダーに比べるとALUの数を増やしたからといって性能が上がりやすいわけではないが、減らしたというのはちょっと想定外だった。これにより効率は上がりつつ、性能を落とさないどころかむしろ引き上げているというのが驚異的ではある。

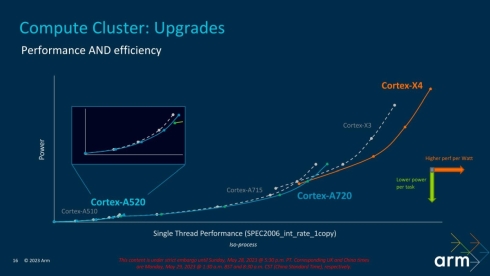

3種類のコアの性能と消費電力の関係をまとめたのが図11である。きれいに3種類のコアが最小限のオーバーラップで推移しているのが分かるかと思う。

図11 横軸はSPEC CPU2016_int-rateの結果なので、Cortex-A510とCortex-A520ではそれほどの差が見られないが、少なくとも遅くなっていないのは事実である[クリックで拡大]

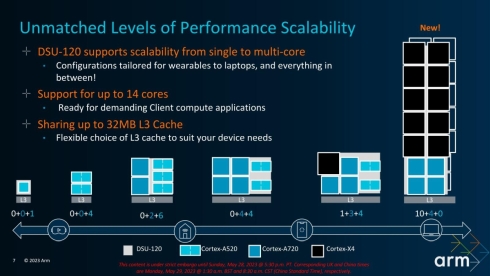

これらのCPUコアでDynamIQを構成するためのプロセッサインターコネクトがDSU-120であるが、従来の「DSU-110」からの変更点として以下のような項目が挙げられている(図12)。

- 1コアから最大14コアまで構成可能

- 最大32MBのL3をサポート

- キャッシュミス時のDynamic Powerを18%、通常のL3アクセスのDynamic Powerを7%、それぞれ削減

- intuitive power modeを新しく搭載してリーク電流削減を可能にした

- Bandwidth Partitioning、Max Power Mitigationなどの機能を追加。これに合わせて新しいインタフェースを搭載

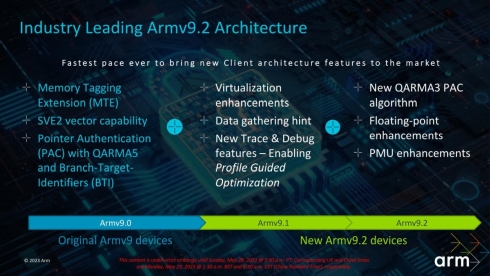

一方、命令セットに目を向けると、先に挙げたようにArmv9.2aに完全対応しているのが特徴である。この拡張命令セットの詳細は連載第14回で説明しているが、QARMA(Qualcomm ARM Authenticatorの略)をベースにしたPAC(ポインタ認証コード)やMTE(Memory Tagging Extension)などは基本的にはArmv9.0aで実装されており、これを拡張したりFPUやVirtualizationなどを強化したり、といった内容が主ではある(図13)。

ただ実はソフトウェアエコシステムはこのPACやMTEへの対応がちょっと遅れており、今回のTSC23の発表に合わせて各社からPACやMTEを含むArmv9.2a対応のコンパイラやデバッガなどのアナウンスがあったあたりは、やっとこれからこの方式が広く利用されていくのかと思われる。

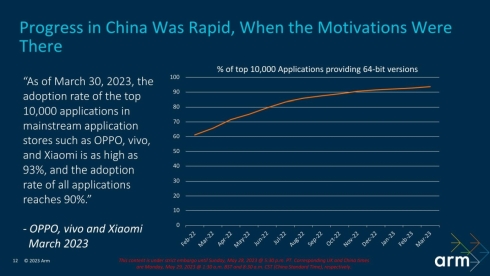

最後に32ビットの廃止について。実はTCS22でも、ハイエンドのCortex-X3やメインのCortex-A715は既に32ビットモードを廃していたが、ローエンドのCortex-A510には32ビットモードのサポートがあった。ところがTCS23で発表されたCortex-A520は、この32ビットサポートを廃している。これに関しては「既にエコシステムのほとんどが64ビットに移行しており、もはや32ビットをサポートする必要がない」というのがArmの見解である(図14)。

Copyright © ITmedia, Inc. All Rights Reserved.