量子コンピュータのCMOSへ、東芝がダブルトランズモンカプラで精度を大幅向上:量子コンピュータ(1/2 ページ)

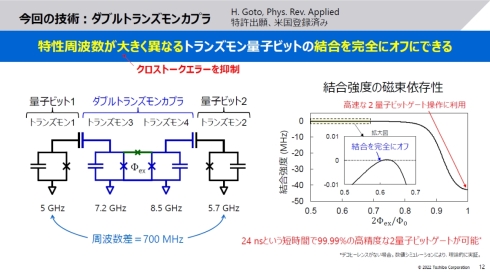

東芝が超伝導回路を用いたゲート方式量子コンピュータの高速化と精度向上を可能にする可変結合器の新構造「ダブルトランズモンカプラ」を考案した。量子コンピュータの基本操作の一つである2量子ビットゲートについて、24nsという短いゲート時間で99.99%という高い精度(誤り確率0.01%)のゲート操作が可能になるという。

東芝は2022年9月16日、超伝導回路を用いたゲート方式量子コンピュータ(超伝導量子コンピュータ)の高速化と精度向上を可能にする可変結合器の新構造「ダブルトランズモンカプラ」を考案したと発表した。量子コンピュータの基本操作の一つである2量子ビットゲートについて、数値シミュレーションベースではあるものの、24nsという短いゲート時間で99.99%という高い精度(誤り確率0.01%)のゲート操作が可能になるという。従来の超伝導量子コンピュータでは、ゲート時間12nsに対して精度は99.6%(誤り確率0.4%)であり、大幅に精度を向上(誤り確率を改善)できることになる。今後はオープンに開発パートナーを募り、2022年度中にダブルトランズモンカプラの試作と実証実験を開始したい考えだ。

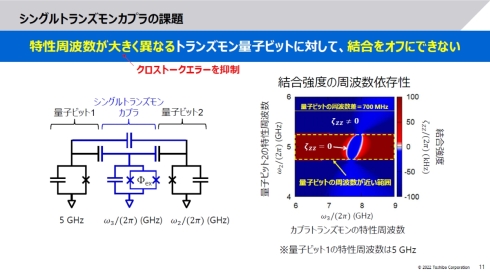

今回東芝が考案したダブルトランズモンカプラは、超伝導量子コンピュータで標準的に用いられている「トランズモン量子ビット」を2つ用いた2量子ビットゲート操作において、量子ビット間の結合のオン/オフを切り替える結合器(カプラ)である。これまでは、周波数が異なる2つのトランズモン量子ビットの間に、周波数を可変できるトランズモン量子ビットと同様の構造を持つ可変結合器を1つ組み込む「シングルトランズモンカプラ」が一般的だったが、2つのトランズモン量子ビットの特性周波数が近い必要があり、この場合にはクロストークエラーに敏感になってしまうことが課題だった。

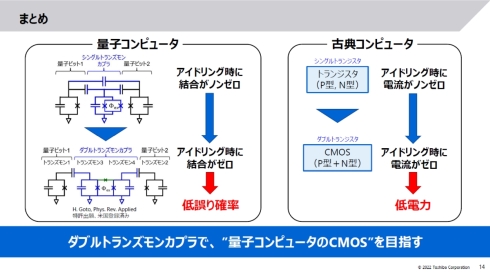

ダブルトランズモンカプラは、2つの可変結合器の間をトランズモン量子ビットに用いられるジョセフソン結合でつなぐような構造をとっている。これにより、クロストークエラーを抑制できる特性周波数が大きく異なる2つのトランズモン量子ビットの結合を完全にオフにできるようになった。東芝 研究開発センター ナノ材料・フロンティア研究所 フロンティアリサーチラボラトリー フェローの後藤隼人氏は「古典コンピュータの進化は、アイドリング時に電流が流れず低消費電力が可能になる、P型とN型のトランジスタを組み合わせたダブルトランジスタ構造のCMOSの登場がきっかけとなった。アイドリング時に結合が完全にオフ(ゼロ)となり、従来よりも誤り確率を大幅に低減できるダブルトランズモンカプラは量子コンピュータのCMOSを目指せると考えている」と語る。

Copyright © ITmedia, Inc. All Rights Reserved.