第51回 ウェアラブル機器とエンベデッドパッシブ:前田真一の最新実装技術あれこれ塾(1/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第51回はウェアラブル機器とエンベデッドパッシブについて解説する。

1.ICのコスト

ICの価格では、チップ(ダイ)のコストが大きな割合を占めています。ICチップの歩留まりや、ダイの面積が話題になるのはそれが価格に大きく結びついているからです。

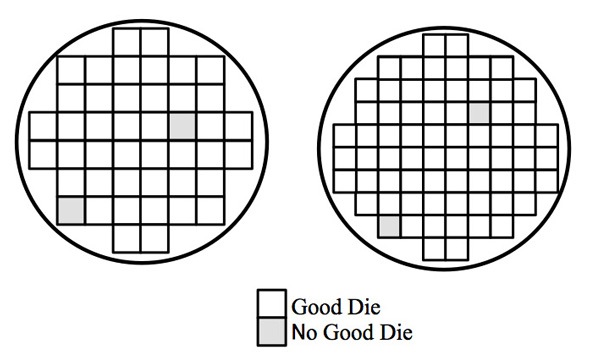

ダイの面積が小さくなれば、1枚のウエハーから取れるダイの数が多くなると同時に歩留まりも向上します(図1)。

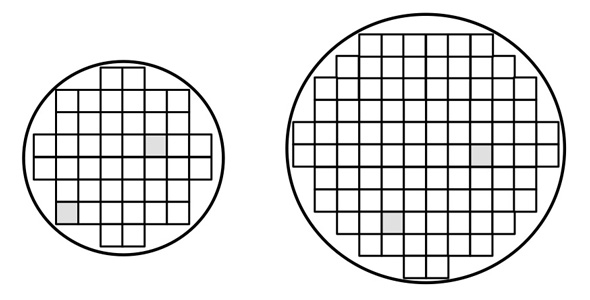

同様にウエハーのサイズが大きくなれば、1枚のウエハーから取れるダイの数が多くなり、ダイ1個当たりの価格が安くなります(図2)。

このため、メモリなどのように同じ機能のICを長期にわたり作り続ける場合、製造技術の進歩に従い、微細化してダイサイズを小さくするシュリンク化が行われます。

しかし、ICはシリコンチップのままでは、基板には実装できません。一部の例外を除いてはICチップはパッケージング(封止)された形で流通し、基板へ実装されます。このパッケージは、ダイのパッドから基板のピン(ボール)への配線をするためのインタポーザとダイを封止し、ダイの保護とダイが発生する熱を効率良く放熱します。

また、IC内部の回路動作による急激な消費電力の変化を抑えるためのオン・パッケージ・コンデンサなどの回路部品や実装もパッケージコストになります。要するに、部品としてのICのコストで、ダイ以外のコストがパッケージコストとなります。

これまでは、このパッケージングのコストは非常に高価であり、安いコストで信頼性を高くすることが、パッケージング技術の大きな開発目標でした。

リードフレームにプラスチック封止を行うICではパッケージコストは微々たるもので、ICコストの90%以上はダイのコストとなっています。

しかし、近年はICのコストでパッケージが占める割合が急速に大きくなってきました。ICの端子が急激に増え、また、消費電力が膨大になるにつれ、ICのパッケージコストが上がり、場合によってはダイのコストより、パッケージのコストの方が高くなっている場合もあります。

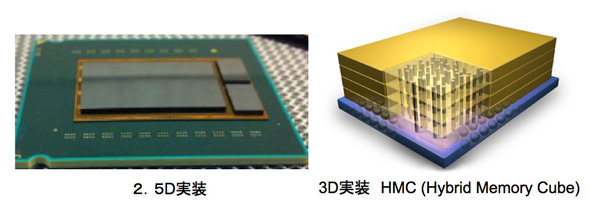

今後、TSVによるダイの2.5次元実装や3次元実装が多くなれば、パッケージングコストの割合はますます大きくなっていきます(図3)。

例えば、あるパッケージング会社のエンジニアは、「TSV製造技術は確立され、量産化することは可能だが、TSVのコストを吸収できる高付加価値製品が少ないので普及していない」と言っています。

Copyright © ITmedia, Inc. All Rights Reserved.