第29回 3次元実装と熱:前田真一の最新実装技術あれこれ塾(2/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第29回は、採用が広がりつつある3次元実装と熱の関係について取り上げる。

2. 3次元実装と熱

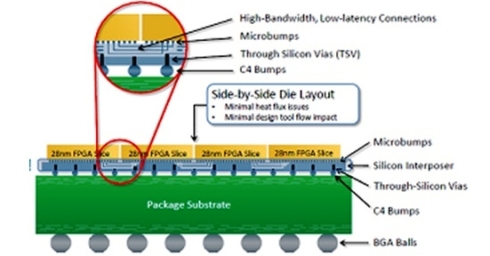

TSV(Through Silicon Via)が徐々に実用化され、XilinxやAlteraなどの製品に使われています。

しかし、これらの製品は当初、TSV技術が目指した3D実装ではなくTSVを誓ったシリコン基板上に平面的にICチップを配置した平面実装です(図5)。

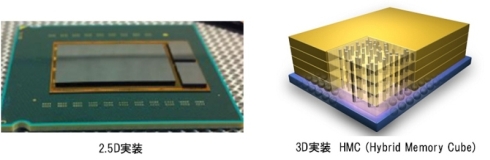

このようなシリコンインタポーザにTSVを使ったMCM(Multi Chip Module)をチップを積層した3D実装に対して2.5D実装と呼ぶようになりました(図6)。

現在、チップの3次元実装で最も大きな問題は、熱とチップ供給電源の安定です。

シングルチップでも熱と電源の同時スイッチングノイズ(SSOノイズ)が大きな問題になっています。3D実装でチップが同一面積で複数積層されると、単位面積あたりの発熱はそれだけ増大します。

3D実装では配線が短くなり、伝送信号の品質はよくなります。チップ間を行き来する信号のドライバは配線が短いため、電流を大幅に減少することができます。このためIO電流は削減し、この部分の消費電力は減少できます。例えば、今、直近の3D実装対象になっているメモリシステムではこのIO電流の削減は大きな効果があります。

CPU周りのバスではメモリバスの消費電力が非常に大きな割合を占めています。インテルの新しいCPUチップ、Haswellでは省電力を最大の目標に開発されました(図7)。グラフィックのキャッシュメモリをeDRAMとしてCPUチップと同じパッケージにMCM化しています。

ICの消費電力はIOだけではなく、内部クロックや論理回路の消費電力も多くを占めています。

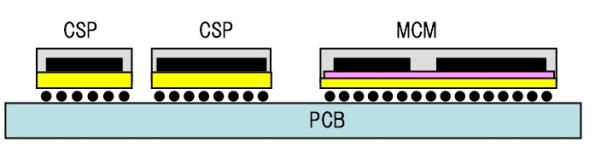

2.5D実装ではチップは2次元的に配置されるため、単位面積当たりの消費電力は個々のICをCSP(Chip Size Package)で個別部品とした場合とあまり変わりありません(図8)。

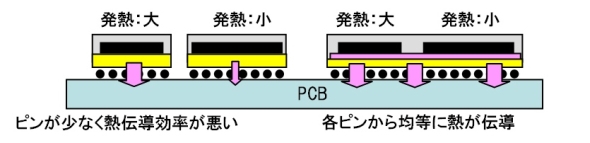

シリコンインタポーザは一般のガラスエポキシに比べ、熱伝導率が飛躍的に高くなっています。さらに、MCMは基板と違って配線長さが短く、決まっていますので、IOドライバの電流値も最適化できます。このため、インタポーザを使った2.5D実装は、一般のCSPよりも熱設計的には有利といわれています(図9)。

また、ICの3D実装ではパッケージ面積が小さく電源、GNDピンを増やすことが困難ですが、2.5D実装ではパッケージ面積が大きく、ピン数を増やすことが可能です。 外部との信号接続の信号数は同じなので、ピン数を多くすることは電源・GNDピンを増やすことになります。

電源・GNDのピン数を増やすと電源供給ネット(PDN)のLとRが並列接続となり、電源ノイズが減少するだけでなくピンを介してパッケージの熱が基板に伝導され、パッケージの冷却にも効果が大きくなります。

これが現在、2.5D実装が主流で3D実装が実用化するまでは、あと2〜3年かかるといわれている理由です。

2.5D実装でTSV製造のコストや信頼性、歩留まり、電気特性などを高める実用化技術を進歩させながら、3D実装のための熱問題を製品レベルまで解決してゆくのがマイルストーンとなります。

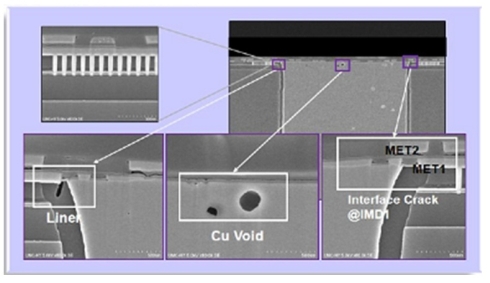

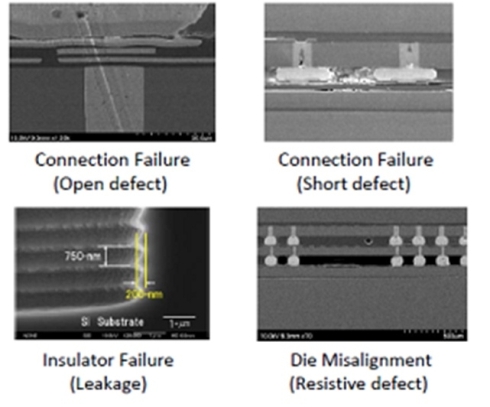

このため、ここ数年、多くの3D実装に関した熱問題や応力、接続信頼性に関する研究がされています(図10、図11)。

Copyright © ITmedia, Inc. All Rights Reserved.