第26回 TSV実用化に向けて:前田真一の最新実装技術あれこれ塾(2/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第26回は、第25回に引き続きTSV(Through Silicon Via)について取り上げる。話題先行で実用化までまだ時間がかかると思われているTSVだが、ソニーの裏面照射CMOSセンサーの新製品にはTSVが適用されているのだ。

2. 実用化へ向けてのTSV環境

実験室や試作レベルの製造と、製品レベルの製造の間には大きな技術的な差があります。

現在、多くの会社がTSV技術を開発したり、評価したりしています。しかし、この中の多くが、本格的な製品に展開するのに2〜3年が必要だとしているのは、この試作から実用への技術展開の時間にあたります。

まず製品化と普及に際して最も重要なことは製造コストです。Xilinx社でもシステムを巨大な1チップに集積したLSIを製造するよりは小さな複数チップに分割して、TSVを使った2.5次元実装のほうが安くできるという理由で2.5次元実装を製品化しました。

製造コストには、製造装置への設備投資、製造にかかる時間、歩留まりが大きな要素になります。TSVはLSIの微細化に比べて微細露光やトランジスタの3D化など莫大な設備投資や技術投資は必要ありません。

しかし、TSVに特化した装置は必要です。このため、東京エレクトロンをはじめ、製造装置会社がTSV用製造装置を発表しています*1)。

*1)東京エレクトロンの2011年12月6日付けニュースリリース

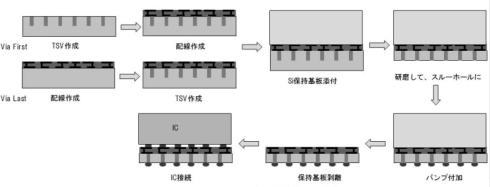

例えば、TSVの穴あけ装置です。TSVでは高アスペクト比の深い穴をあける必要があります。この穴あけ時間の短縮はそのまま製造時間の短縮で製造コストの低減になります。穴あけ後、穴内部の導通作成、補強シリコンと貼り合わせての研磨、補強シリコンの剥離などTSV作成の独自工程は多くあります(図7)。この各工程での所要時間と歩留まりが製造コストと品質に直接反映されます。

例えば、保持用のシリコンとTSV基板の貼り合わせでは研磨時にしっかりと保持し、ずれや傾きが生じないようにする必要がありますが、研磨が終わった後には薄い研磨済の基板を割らないように簡単に保持基板から剥離する必要があります。研磨は高速に厚さむらがなく平坦に行う必要があります。

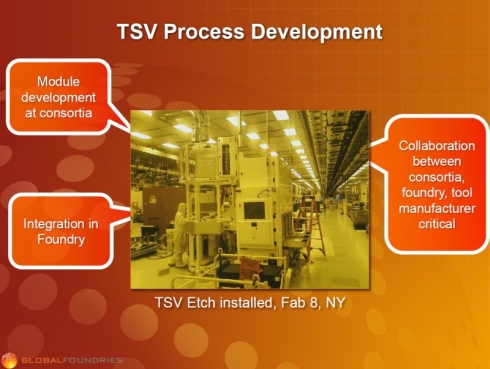

ECTC2012では、GLOBALFOUNDRIESがNYのFab 9にこれらTSV製造装置をそろえ、TSV製造ラインを作ったと発表しています(図8)。

Copyright © ITmedia, Inc. All Rights Reserved.