第25回 量産技術化が進むTSV:前田真一の最新実装技術あれこれ塾(3/4 ページ)

実装分野の最新技術を分かりやすく紹介する前田真一氏の連載「最新実装技術あれこれ塾」。第25回は、量産技術として開発が加速しているTSV(Through Silicon Via)の最新動向を解説する。

3. TSVの実用化

まだ、学会発表や試作段階のTSVではありますが、TSVがまったく市場に出ていないかというと、そうではありません。

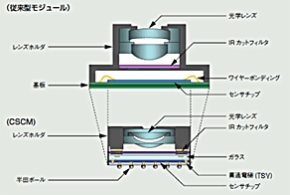

図12 TSVを使ったイメージセンサカメラモジュールの構造イメージ(岩手東芝エレクトロニクス http://www.toshiba-iwashiba.co.jp/product/cscm.htm#TSV)

東芝やソニーでは、CMOSイメージセンサと論理ICをTSV接続した商品を量産しています(図12)。

また、FPGAではAlteraとXilinxがTVSを使った2.5次元実装が製品化しています(図13、図14)。

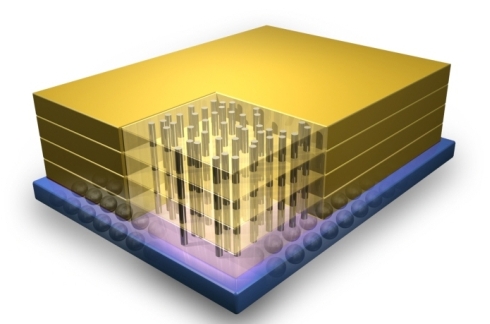

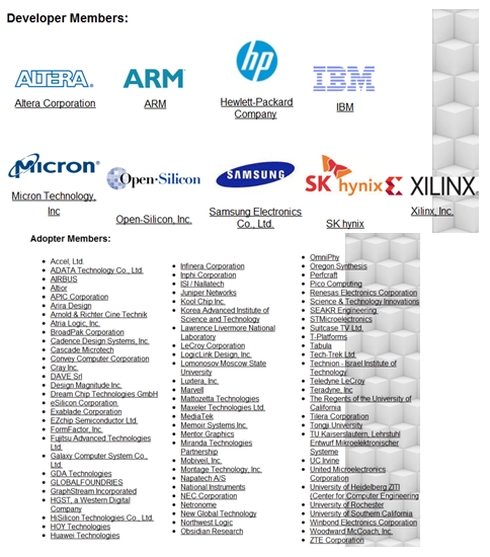

IBMとMicron TechnologyがHMC(Hybrid Memory Cube)(図15)を発表し、現在はSamsungやHP、ARMなどとコンソーシアムを作成しています(図16)。

このように一部は実用化されてきたTSVですが、まだメインストリーム製品への本格的な商品化はされていません。

今年1月のネプコンセミナーでIntel社と米Qualcomm社は講演においてTSVを使ったチップの3次元実装が2015〜2016年に実用化される、としていました。

このスケジュールだと、今年、2013年から来年前半にかけてはTVSは各社、量産と検査、評価技術が確立される時期にあたります。

米国各社は、このような技術のめどが立っていることに基づき、2015〜2016年に実用化を発表していると思われます。

4. TSVの技術発表動向

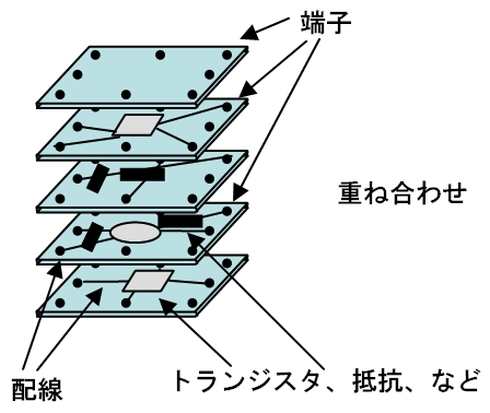

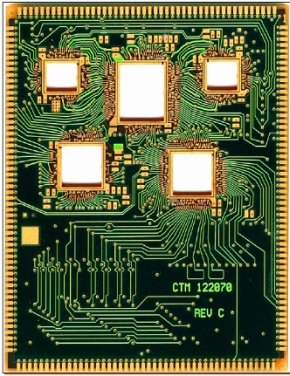

アメリカでは1990年頃にシリコンインタポーザ使ったマルチ・チップ・モジュール(MCM-D)が多く現れました。これは現在の2.5次元実装です。

MCM自身は1960年代、IBM System360でセラミック基板に複数の部品を実装し、モジュールとして基板上に実装したものが初め(図17)で、その後、高周波回路などによく使われていました(図18)。

それが、セラミック基板の代わりに安価なプリント配線板や高機能なシリコン基板を使って、SiPを実現する流れが90年代になって出てきたのです。

シリコンインタポーザを使ったMCM-Dはその配線の集積密度の高さや、チップと基盤の熱膨張率が同じで熱応力が小さいこと、放熱特性が良いことなど高性能化では群を抜いていましたが、価格やビアを使っての電源供給の困難さなどの技術的問題がありました。

このため、日、米、欧でシリコンインタポーザビア接続する技術(TSV)の研究開発が進められました。

最近では急速にアジアの研究機関がTSVの開発を進めています。

日本では、超先端電子技術開発機構(ASET)が1999年度から『超高密度電子SI』というプロジェクトを開始しました。

1990年代から2000年代の始めまでは、ヨーロッパを始めとして、各国から学会レベルで、シリコンに貫通ビアをあけて導通を確保したという発表が多くありました。この頃の発表はTSVに対する個別技術が主体でした。つまり、穴あけの方法、ビアの導通の作り方、シリコン基板の平坦化技術、インタポーザとICチップの接続技術などです。

その後、信頼性、熱特性など、実用化に向けてのアプローチもありましたが、価格の問題があり、特に日本では、一部のハイエンド製品にしかマーケットがないのではないかとの考えも出てきました。

Copyright © ITmedia, Inc. All Rights Reserved.