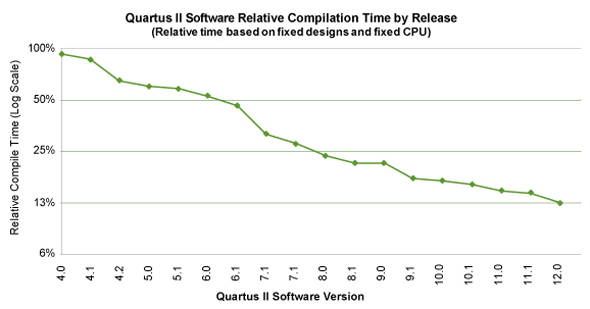

28nm世代FPGAのコンパイルが4倍高速に! アルテラ「Quartus II v12.0」発表:設計生産性がさらに向上

アルテラは、CPLD/FPGA/ASIC用の開発ツール「Quartus II」の最新版となる「Quartus II v12.0」を発表。前バージョンと比較して、28nmFPGAのコンパイル時間を最大4倍高速化できるという。

FPGA大手ベンダーのアルテラは2012年6月12日(米国時間)、CPLD/FPGA/ASIC用の開発ツール「Quartus II」の最新版となる「Quartus II v12.0」を発表した。

Quartus II v12.0の「サブスクリプション・エディション」と無償の「ウェブ・エディション」は、どちらもアルテラのWebサイトから入手可能である。

Quartus II v12.0では、28nm世代のFPGA製品におけるコンパイル時間のさらなる高速化が図られている。Quartus IIの前バージョンと比較して、「Stratix V」ユーザーはコンパイル時間を平均35%削減でき、内部クロック周波数(Fmax)も向上するという。「Cyclone V」「Arria V」ユーザーについては、平均25%のコンパイル時間の削減が期待できるとする。

さらに今回、アームのプロセッサコア「Cortex-A9 MPCore」をハードIPとして集積するFPGA製品群「SoC FPGA」ファミリの1つである「Cyclone V SoC」を初めてサポートする他、28nm世代のFPGA製品(Stratix V、Cyclone V、Arria V)に対する設計サポートが拡大されている(表1)。

| Stratix V GXおよびStratix V GS量産デバイス向けの プログラミングサポート |

5SGXA7、5SGXA4、5SGXA3、5SGXA5 5SGSD5、5SGSD4 |

|---|---|

| Stratix V GT FPGAのプログラミングサポート | 5SGTC5 |

| Arria V FPGAファミリで最大規模となるArria V GT FPGA | 5AGTD7 最終版のピン配置情報 |

| Cyclone V FPGAデバイスサポート | 5CEA7、5CGTD7 5CEA9、5CGXC9、5CGTD9 |

| Cyclone V SX SoC FPGA(コンパイルサポート) | 5CSXFC6D6 |

| 表1 Quartus II v12.0では28nm世代のFPGAに対するサポートを拡大 | |

Quartus II v12.0のリリースに併せ、アルテラのシステム統合ツール「Qsys」も強化。アームの標準インタフェース「AMBA AXI-3」のサポートに加え、システムスクリプトAPIやPCI Express Gen3 x4 IPのサポートなどがなされている。

その他にもQuartus II v12.0では、DSP設計ツール「DSP Builder」の機能拡張や、IPコア製品群の改良などが含まれるている(Quartus II v12.0の新機能について)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

- >>「FPGA」コーナー

- 連載記事「FPGA Watch」

FPGA業界で今何が起きているのか? シリコンテクノロジーの収束

FPGA業界で今何が起きているのか? シリコンテクノロジーの収束

日本アルテラは、東京・秋葉原で「アルテラ・エンベデット・サミット(Altera Embedded Summit)」を開催。オープニングセッションに登壇した日隈寛和社長の講演「ムーアの法則を超えて 〜Technology Convergence〜」の内容をお届けする。