ニュース

Polyspace解析技術を搭載した「Simulink Design Verifier 2.0」を発表、MathWorks:Simulinkモデルで自動エラー検出を可能に

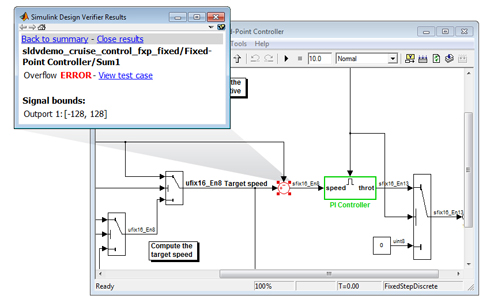

MathWorksは、Simulinkモデルで自動エラー検出を可能にするため、「Simulink Design Verifier」にPolyspace解析技術を搭載した「Simulink Design Verifier 2.0」を開発し、提供を開始する。

MathWorksは2011年7月7日(米国時間)、Simulinkモデルで自動エラー検出を可能にするため、「Simulink Design Verifier」にPolyspace解析技術を搭載した「Simulink Design Verifier 2.0」を開発し、提供を開始すること(価格は120万円〜)を発表した。

同製品では、Polyspaceエラー検出機能が既存のプロパティ検証やテスト生成機能と統合されるため、設計エラーの根本的原因の発見や修正にかかる時間を短縮できる上、検証と妥当性確認にかかる全体的なコストの削減を可能にするという。

航空宇宙、自動車、医療、産業オートメーション、および産業機械の各分野において、同製品が提供する形式的解析手法を使用し、モデルベースデザインを適用することで、詳細なテストやシミュレーションを行わなくても、SimulinkモデルやStateflowモデルの設計上の欠陥を特定できるようになるとしている。

以下に、同製品の特長を示す。

- デッドロジック、整数や固定小数点のオーバーフロー、ゼロ除算、アサーション違反などを検出

- 機能的な要求仕様やセキュリティに関する要求仕様をモデリングするためのブロックや関数

- 機能的な要求仕様とモデルカバレッジの目標から、ベクトル生成をテスト

- 解析とデバッグのために違反の例を生成し、プロパティを検証

- 固定小数点と浮動小数点のモデルをサポート

Copyright © ITmedia, Inc. All Rights Reserved.

いまさら聞けない モデルベース開発入門

いまさら聞けない モデルベース開発入門 トヨタとデンソー、量産開発に適用しているMATLABのバージョンを「R2010b」へ移行

トヨタとデンソー、量産開発に適用しているMATLABのバージョンを「R2010b」へ移行